# YAŞAR UNIVERSITY GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

## PHD THESIS

# FPGA BASED CONTROL AND RECONFIGURABLE

# **MECHANISM IN WSN**

# AHMED KHAZAL YOUNIS, AL-AZZAWI

## THESIS ADVISOR: ASSOC. PROF. TUNCAY ERCAN

COMPUTER ENGINEERING

PRESENTATION DATE: 03.05.2019

BORNOVA / İZMİR MAY 2019 We certify that, as the jury, we have read this thesis and that in our opinion it is fully adequate, in scope and in quality, as a thesis for the Doctor of Philosophy.

#### Jury Members:

#### Signature:

Assoc. Prof. Dr. Tuncay ERCAN Yaşar University

Prof. Dr. Mehmet ÜNLÜTÜRK Yaşar University

Assoc. Prof. Dr. Y. Murat ERTEN Izmir Institute of Technology

Asst. Prof. Dr. Samsun BAŞARICI Adnan Menderes University

Asst. Prof. Dr. Mahir KUTAY Yaşar University

(110 be)

Prof. Dr. Cüneyt GÜZELİŞ Director of the Graduate School

#### ABSTRACT

## FPGA BASED CONTROL AND RECONFIGURABLE MECHANISM IN WSN

Al-Azzawi, Ahmed Khazal Younis PHD, Computer Engineering Advisor: Assoc. Prof. Tuncay ERCAN May 2019

Wireless Sensor Networks (WSNs) enable various solutions for many application fields. They have acquired large popularity because of their low cost, scalability, easily distributed and maintainable features compared to the traditional infrastructure of monitoring solutions. Generally, any WSN consists of a huge number of distributed sensor nodes that can measure a specific physical phenomenon, perform required tasks and enable monitoring of infrastructure-less deployment. A wireless sensor node is constrained by its cost, energy, and size. In order to overcome these limitations, this thesis aims to introduce a smart design and multi-tasking for wireless sensor networks by extending the capability of re-configurability and enhancing the computational power of the sensor nodes. These facilities can be integrated in a typical WSN and IoT (Internet of Things) environment by incorporating an FPGA (Field Programmable Gate Array) device. Enhancing the computational power of data analysis is done by integrating multi-core of adaptive neuro-fuzzy algorithms in the FPGA device. This thesis contributes into the scientific knowledge with two new modifications in the ANFIS (Adaptive Neuro-fuzzy Inferences System algorithm) by using the momentum factor that will accelerate the training phase and adding a new hidden layer to decrease the number of adjustable linear parameters in the FPGA resources. The neuro-fuzzy approach is a kind of soft computation systems that combine between the learning capability of artificial neural networks and the powerful inference system in fuzzy logic. These two techniques are utilized in order to deal with complex problems when the traditional methods cannot provide a simple and precise solution. Later, the multihardware cores of the modified algorithms are comprised within the architecture of FPGA by using the different sensor data sets. HW/SW cores in the FPGA are used to perform different tasks such as classification, prediction, alerts, and decision-making.

On the other hand, the modified ANFIS algorithm will extend the capability of MATLAB toolbox for software developers, and the newly generated IP library in the FPGA that will combine multi-server and multi-client devices will be ready to use by researchers in different IoT implementations. The simulation results of the hardware architecture proposed in this thesis provide significant contributions to the state of the art by providing additional insights and a deeper understanding when compared with existing academic and commercial examples.

**Key Words:** adaptive systems, neuro-fuzzy system, re-configurability, ANFIS, FPGA, smart systems, embedded systems, smart control.

## KABLOSUZ ALGILAYICI AĞLAR İÇİN FPGA TABANLI KONTROL VE YAPILANDIRILABİLİR MEKANİZMA

Al-Azzawi, Ahmed Khazal Younis Doktora Tezi, Bilgisayar Mühendisliği Danışman: Doç. Dr. Tuncay ERCAN Mayıs 2019

Kablosuz Algılayıcı Ağlar (KAA) birçok uygulama alanı için farklı çözümler sağlarlar. Bu ağların geleneksel izleme altyapılarıyla karşılaştırıldıklarında sahip oldukları düşük maliyet, ölçeklenebilirlik, kolaylıkla dağıtılabilir olmaları ve sürdürülebilirlikleri nedeniyle kullanımları da oldukça artmıştır. Genel olarak, KAA'lar kullanıldıkları ortamla ilgili olarak fiziksel değişiklikleri ölçebilecek çok fazla sayıda algılayıcı düğümler içerebilir, önceden belirlenmiş görevleri yerine getirebilir ve altyapısı olmayan yerlerde maliyet, enerji ve işlemci gibi kısıtlarına rağmen izleme yapabilirler. Kablosuz bir algılayıcı düğümün maliyet, enerji ve boyut gibi bazı sınırlamalarını kısmen veya tamamen ortadan kaldırabilmek için, bu tezimizde algılayıcı düğümlerin çoklu görevleri yerine getirebilmeleri için işlemci gücünü artıracak, tekrar yapılandırılabilme kabiliyetini yükseltecek akıllı bir tasarım hedeflenmiştir. Bu da tipik bir KAA veya Nesnelerin İnterneti (IoT-Internet of Things) ortamında FPGA (Alan Programlanabilir Kapı Dizisi) cihazlarının kullanılmasıyla gerçekleştirilebilir. Böyle bir ortamda veri analizi için işlemci gücünün arttırılması FPGA cihazı üzerinde uyarlanabilir yapay sinir ve bulanık algoritmaların birlikte çalıştırılmasıyla gerçekleştirilebilir. Bu tez bilimsel bilgiye ANFIS algoritmalarındaki iki yeni değişiklikle katkıda bulunmaktadır. Birincisi veri setlerine olan tanışıklığın sağlandığı eğitim safhasını hızlandıracak momentum faktörünün eklenmesi, diğeri FPGA üzerindeki kaynakların kullanımını etkinleştirecek olan doğrusal parametre sayısını azaltacak ilave bir gizli katmanın eklenmesidir. Sinir-Bulanık yaklaşımlar yapar sinir ağlarındaki öğrenme ve bulanık sistemlerdeki güçlü çıkarım yapabilme yeteneklerini öne çıkartan yazılım tabanlı teknikleri içerirler. Bu iki farklı teknik, geleneksel yöntemlerin basit ve kesin bir çözüm sağlayamadığı karmaşık problemleri

ÖZ

çözebilmeyi mümkün kılmaktadır. Daha sonra değiştirilmiş olan bu algoritmalar farklı veri setlerini kullanarak FPGA mimarisi içinde uygulanır. FPGA içindeki donanım ve yazılım bileşenleri sınıflandırma, kestirme, alarm ve karar verme gibi farklı görevleri yerine getirebilir. Diğer yandan, değiştirilmiş ANFIS algoritması yazılım geliştiriciler için MATLAB araç kutusunun yeteneğini arttıracak, FPGA cihazı üzerinde çoklu-kullanıcı ve çoklu-sunucu ortamları için geliştirilen yeni kütüphane de IoT uygulamalarında araştırmacılar tarafından kullanılmaya hazır olacaktır. Bu tezde önerilen donanım yapısı ile ilgili benzetim sonuçları, akademik ve ticari örneklerle karşılaştırıldığında, mevcut bilgiye ve anlayışa en güncel bilgilerle yeni bir derinlik katıldığını ve önemli bilimsel katkılar sağladığını göstermektedir.

Anahtar Kelimeler: uyarlanabilir sistemler, sinir-bulanık sistem, yeniden yapılandırma, ANFIS, FPGA, akıllı sistemler, gömülü sistemler, akıllı kontrol.

#### ACKNOWLEDGEMENTS

I would like to express my enduring love to my parents, who are always supportive, loving and caring to me in every possible way in my life.

Foremost, I would like to express my sincere gratitude to my advisor Assoc. Prof. Dr. Tuncay Ercan for the continuous support of my Ph.D. study and related research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me a lot in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my Ph.D. study.

Besides my advisor, I would like to thank the rest of my thesis committee: Prof. Dr. Mehmet Ünlütürk and Assoc. Prof. Dr. Y. Murat Erten for their insightful comments, encouragement, and for their hard questions that incented me to widen my research from various perspectives.

Last but not the least; I would like to thank my family: my mother, my wife, and my three wonderful children.

Ahmed Khazal Younis Al-Azzawi Izmir, 2019

### **TEXT OF OATH**

I declare and honestly confirm that my study, titled "FPGA BASED CONTROL AND RECONFIGURABLE MECHANISM IN WSN" and presented as a PhD Thesis, has been written without applying to any assistance inconsistent with scientific ethics and traditions. I declare, to the best of my knowledge and belief, that all content and ideas drawn directly or indirectly from external sources are indicated in the text and listed in the list of references.

Ahmed Khazal Younis Al-Azzawi Signature ..... May 3, 2019

| ABSTRACTiii                                   |

|-----------------------------------------------|

| ÖZ v                                          |

| ACKNOWLEDGEMENTSvii                           |

| TEXT OF OATHVIII                              |

| SYMBOLS AND ABBREVIATIONSXX                   |

| CHAPTER 1 Introduction1                       |

| 1.1 . Research Scope and Objectives           |

| 1.2 . Thesis Outline                          |

| 1.3 . Existing Studies                        |

| Chapter 2 Field Programmable Gate Arrays10    |

| 2.1 . Introduction                            |

| 2.2 . Field Programmable Gate Array Structure |

| 2.3 . FPGA Programming Technologies12         |

| 2.3.1 . FPGA Based SRAM 12                    |

| 2.3.2 . FPGA Based Anti-fuse                  |

| 2.3.3 . EEPROM Based14                        |

| 2.4 . Advantages of using an FPGA14           |

| 2.5 . FPGAs Employed                          |

| 2.5.1 . Xilinx:                               |

| 2.5.1.1 . The Spartan series of FPGAs 15      |

| 2.5.1.2 . The Virtex series of FPGAs 16       |

| 2.5.2 . Altera                                |

### **TABLE OF CONTENTS**

| 2.6 . Xilinx Zinq                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.6.1 . System-on-Chip with Zynq                                                                                                                                             | 19 |

| 2.6.2 . Processing System (PS)                                                                                                                                               | 21 |

| 2.6.3 . The External Interfaces of Processing System                                                                                                                         | 23 |

| 2.6.4 Programmable Logic                                                                                                                                                     | 25 |

| 2.6.5 . Programmable Logic and Processing System Interfaces                                                                                                                  | 27 |

| 2.6.6 . Advanced eXtensible Interface (AXI)                                                                                                                                  |    |

| 2.7 . WSN based FPGA background and literature review                                                                                                                        |    |

| 2.7.1 . SoC-based FPGA prototype                                                                                                                                             | 29 |

| 2.7.2 . FPGA as a standalone processing unit                                                                                                                                 | 31 |

| 2.7.3 . PLD as MCU co-processing unit:                                                                                                                                       |    |

| Chapter 3 Artificial Neural Networks And Fuzzy System                                                                                                                        |    |

| 3.1 . Introduction                                                                                                                                                           |    |

| 3.2 . How Artificial Neural Networks Work                                                                                                                                    |    |

| 3.3 . Elements of Neural Networks                                                                                                                                            |    |

| 3.3.1 . Weighting Factors:                                                                                                                                                   |    |

|                                                                                                                                                                              |    |

| 3.3.2 . Summation Function                                                                                                                                                   |    |

| <ul><li>3.3.2 . Summation Function</li><li>3.3.3 . Common Activation Function</li></ul>                                                                                      |    |

|                                                                                                                                                                              |    |

| 3.3.3 . Common Activation Function                                                                                                                                           |    |

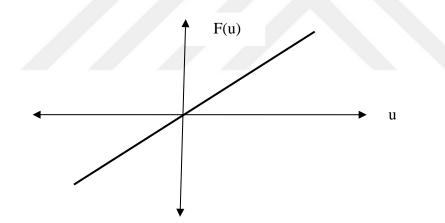

| <ul><li>3.3.3 . Common Activation Function</li><li>3.3.3.1 . Linear Function</li></ul>                                                                                       |    |

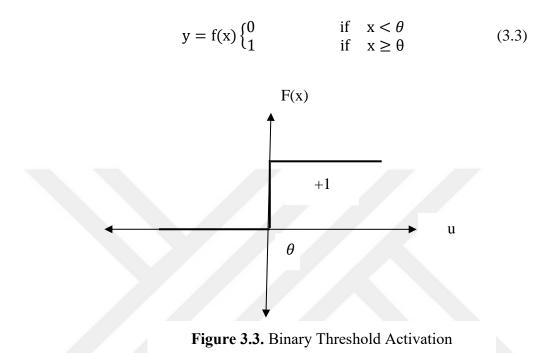

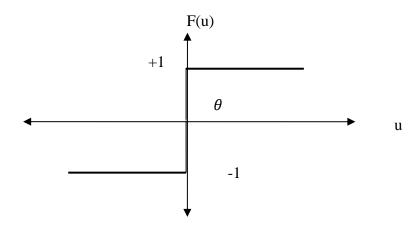

| <ul><li>3.3.3 . Common Activation Function</li><li>3.3.3.1 . Linear Function</li><li>3.3.3.2 . Threshold Function</li></ul>                                                  |    |

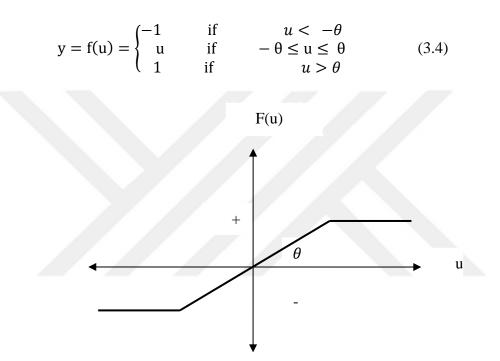

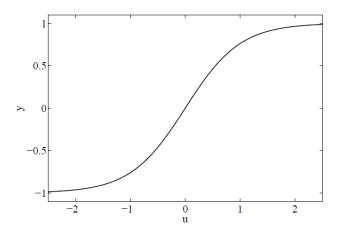

| <ul> <li>3.3.3 . Common Activation Function</li> <li>3.3.3.1 . Linear Function</li> <li>3.3.3.2 . Threshold Function</li> <li>3.3.3.3 . Piecewise Linear Function</li> </ul> |    |

| 3.4.2 . Unsupervised Approach                             |    |

|-----------------------------------------------------------|----|

| 3.5 . Types of Neural Networks                            |    |

| 3.5.1 . Feed-Forward ANN                                  |    |

| 3.5.2 . Feed-back ANN                                     | 43 |

| 3.5.3 . Classification-Prediction ANN                     | 44 |

| 3.6 . Feedforward Back-Propagation                        | 44 |

| 3.6.1 . Learning in Back-Propagation Algorithm            | 45 |

| 3.7 . Network Selection                                   | 50 |

| 3.8 . Neural Networks Applications                        | 51 |

| 3.9 . Introduction to Fuzzy Logic                         |    |

| 3.9.1 . Classic and Fuzzy Sets                            | 53 |

| 3.9.2 . The linguistic variables                          | 56 |

| 3.9.3 . Fuzzy Rules (Reasoning in fuzzy logic)            | 57 |

| 3.9.4 . The Defuzzification                               |    |

| 3.10 Advantages and Disadvantages of Fuzzy Logic system   |    |

| 3.11 . Introduction to Neuro-Fuzzy System                 | 61 |

| 3.11.1 . Types of Neuro-Fuzzy Systems                     | 61 |

| 3.11.2 . Adaptive Neuro-Fuzzy Inference System (ANFIS)    | 63 |

| 3.11.2.1 . ANFIS Architecture                             | 64 |

| 3.11.2.2 . ANFIS Learning Algorithm                       | 66 |

| Chapter 4 ANFIS Modifications                             | 68 |

| 4.1 . Introduction                                        | 68 |

| 4.2 . Effect of Momentum on ANFIS algorithm               |    |

| 4.3 . Performance of Modified Handwritten ANFIS Algorithm | 70 |

| $4.3.1$ . Testing ANFIS performance based on Global Ice Volume data set $\ldots 71$ |

|-------------------------------------------------------------------------------------|

| 4.3.2 . Testing ANFIS Performance based on Time Series Prediction73                 |

| 4.4 . Extended Architecture of ANFIS Algorithm                                      |

| 4.4.1 . Test the Performance of Extended ANFIS Architecture                         |

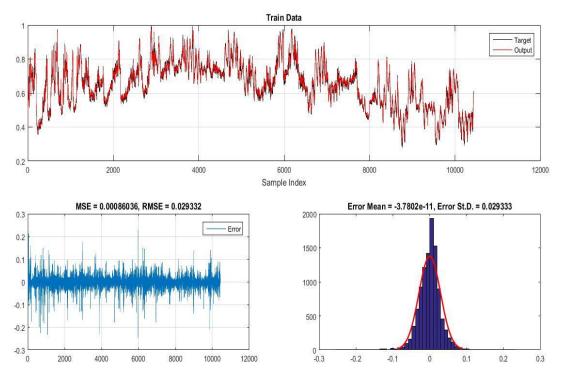

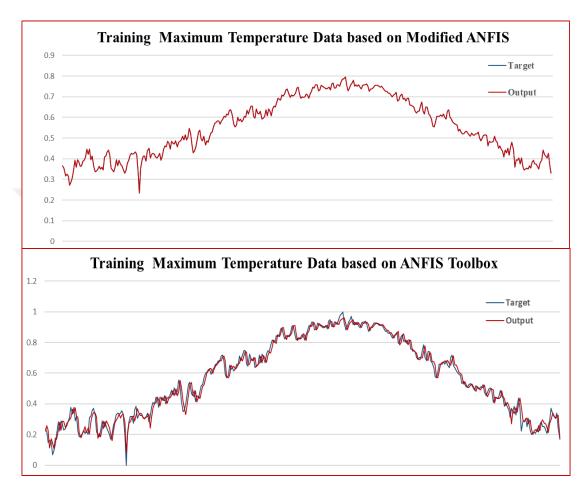

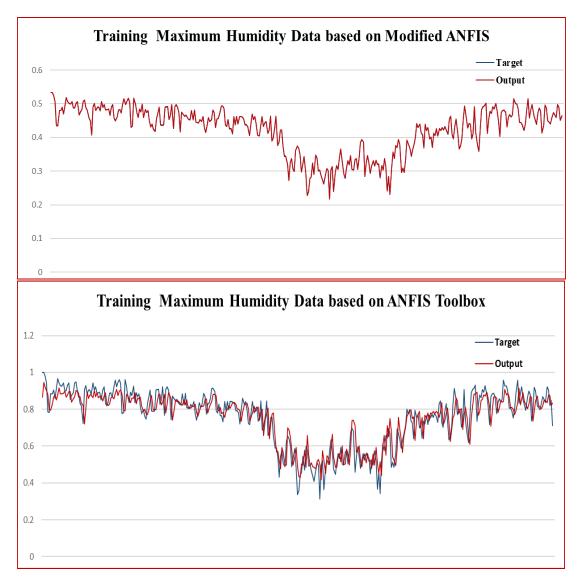

| 4.4.1.1 . Training the Modified Algorithm and ANFIS Toolbox                         |

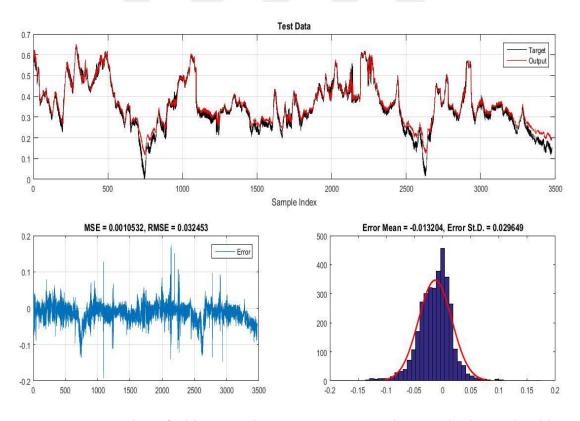

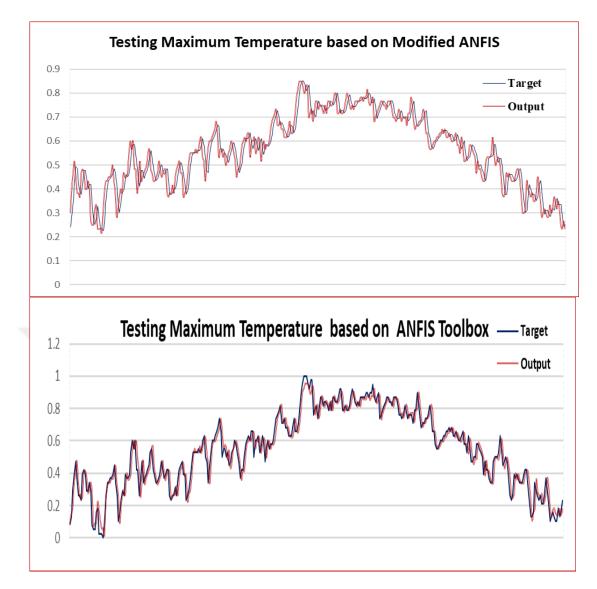

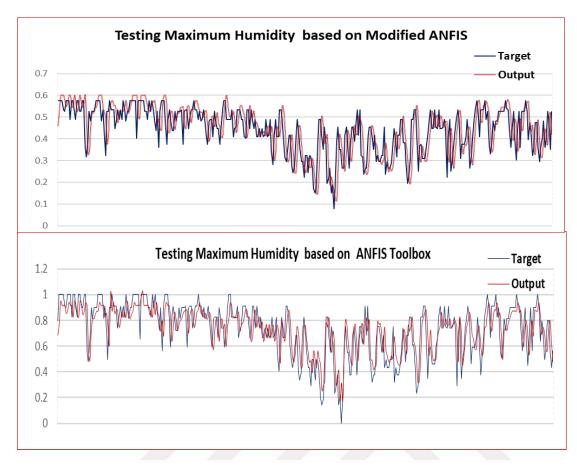

| 4.4.1.2 . Testing Algorithms Using Maximum Temperature and Humidity Sets 88         |

| Chapter 5 Hardware Implementation                                                   |

| 5.1 . Introduction                                                                  |

| 5.2 . Hardware tools                                                                |

| 5.2.1 . Xilinx Vivado Design Suite                                                  |

| 5.2.2 . Xilinx Software Development Kit (SDK)                                       |

| 5.2.3 . Vivado High-Level Synthesis (HLS)                                           |

| 5.3 . Hardware Design                                                               |

| 5.4 . Hardware Test and Results101                                                  |

| Chapter 6 Smart Automation System104                                                |

| 6.1 . Introduction104                                                               |

| 6.2 . Principle of Smart Automation System104                                       |

| 6.3 . Designing of Automation Control System106                                     |

| 6.3.1 . Aggregation Unit107                                                         |

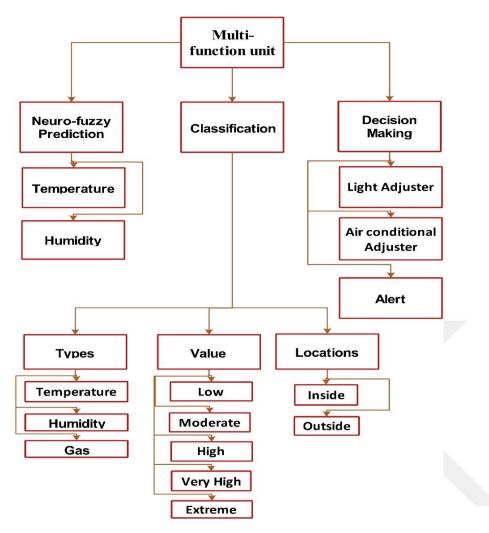

| 6.3.2 . Multi-function unit                                                         |

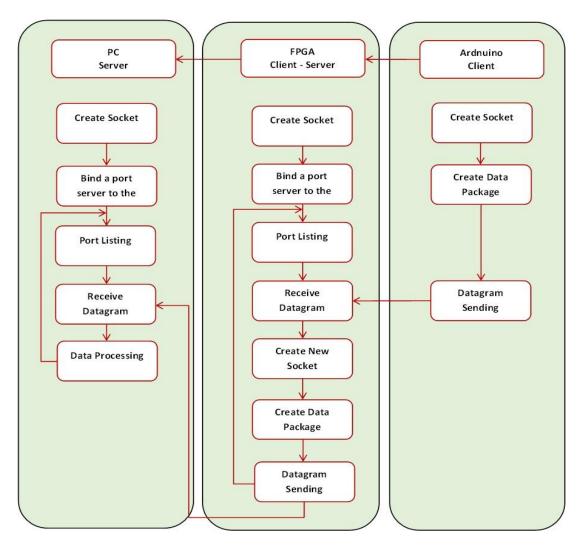

| 6.3.3 . Communication Unit113                                                       |

| 7.3.3.1 . Xilinx Adapter Functions                                                  |

| 6.4 . Experimental Results                                                          |

| Chapter 7 Conclusion And Future Works 124                                           |

| 7.1 . Conclusion                                                                      |  |

|---------------------------------------------------------------------------------------|--|

| 7.2 . Future Works                                                                    |  |

| Appendix A                                                                            |  |

| A.1. Training the Modified Algorithm and ANFIS<br>Temperature and Humidity Data Sets  |  |

| A.2. Testing the Modified Algorithm and ANFIS 7<br>Temperature and Humidity Data Sets |  |

| A.3. Training and Testing Execution Time                                              |  |

### LIST OF FIGURES

| Figure 1.1. Outline of the Thesis                      | 5 |

|--------------------------------------------------------|---|

| Figure 2.1. General Structure of Reconfigurable FPGA   | 1 |

| Figure 2.2. Simplified Routing in FPGA Architecture    | 2 |

| Figure 2.3. Static Memory Cell                         | 3 |

| Figure 2.4. AND/OR Structure Based on Antifuse         | 4 |

| Figure 2.5. Diagram of the System-on-Chip              | 0 |

| Figure 2.6. Internal Architecture of Zynq Device       |   |

| Figure 2.7. Diagram of the Zynq PS22                   | 2 |

| Figure 2.8. Location of the NEON engine within the APU | 3 |

| Figure 2.9. MIO and EMIO Interface                     | 4 |

| Figure 2.10. Zynq PL structure                         | б |

| Figure 2.11. SoC-based FPGA prototype                  | 0 |

| Figure 2.12. FPGA as standalone processing unit        | 1 |

| Figure 2.13. PLD as MCU co-processing unit             | 3 |

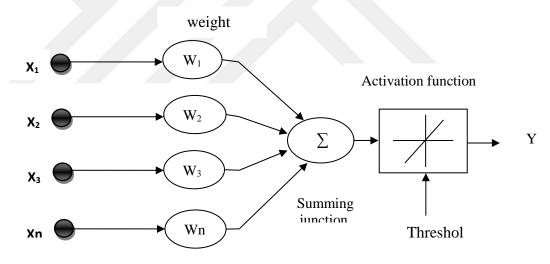

| Figure 3.1. Basic Elements of an Artificial Neuron     | 7 |

| Figure 3.2. Linear Activation Function                 | 8 |

| Figure 3.3. Binary Threshold Activation                | 9 |

| Figure 3.3. Binary Threshold Activation                | 9 |

| Figure 3.4. Bipolar Threshold Activation               | 9 |

| Figure 3.4. Bipolar Threshold Activation               | 9 |

| Figure 3.5. Piecewise Linear Activation Function       | 0 |

| Figure 3.6. Tangent Activation Function                             |

|---------------------------------------------------------------------|

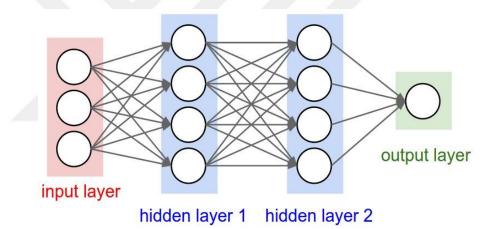

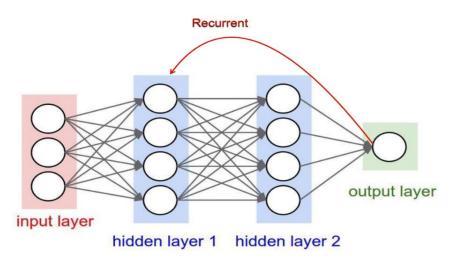

| Figure 3.7. Multi-layer Feed-Forward ANN                            |

| Figure 3.8. Multi-layer Feed-back ANN                               |

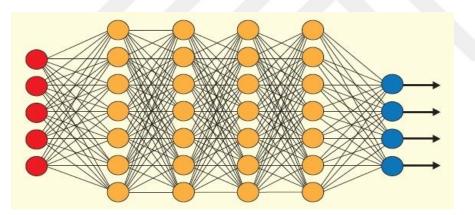

| Figure 3.9. Multi-output Feed- Forward ANN                          |

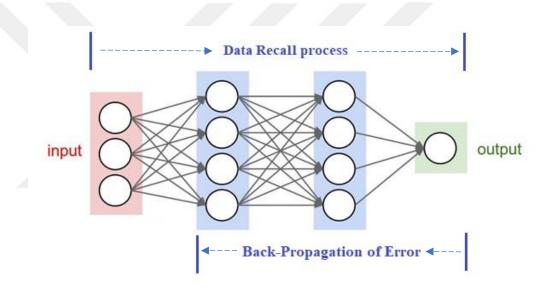

| Figure 3.10. Example of Typical (BP) Architecture                   |

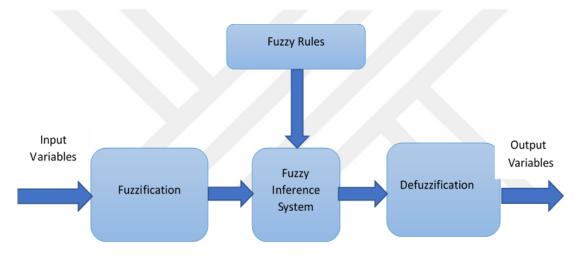

| Figure 3.11. Architecture of Fuzzy Logic System                     |

| Figure 3.12. Relationship between Fuzzy and Classic SetsCrisp Logic |

| Figure 3.12. Relationship between Fuzzy and Classic Sets            |

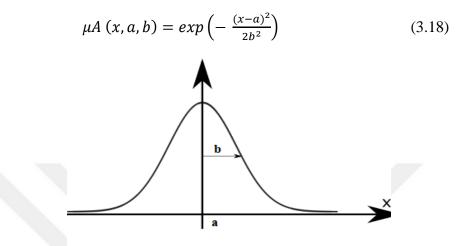

| Figure 3.13. standard Gaussian Membership                           |

| Figure 3.14. General Form of Trapezoidal Membership55               |

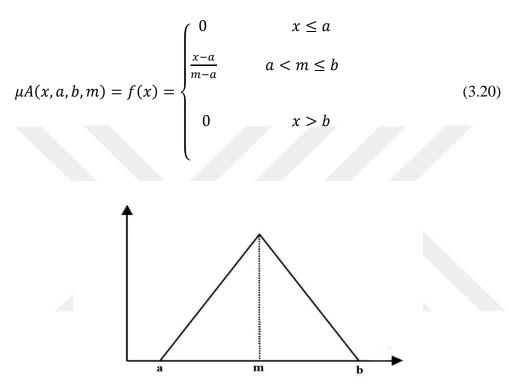

| Figure 3.15 General Form of Triangular function                     |

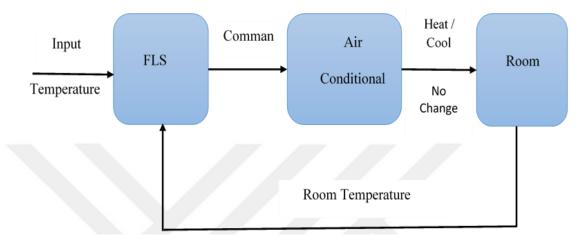

| Figure 3.16. Air Conditioner based on Control of Fuzzy Logic System |

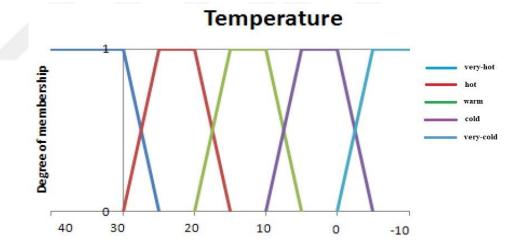

| Figure 3.17. The Linguistic Terms of the Temperature                |

| Figure 3.18. Mean of Maxima Defuzzification Method                  |

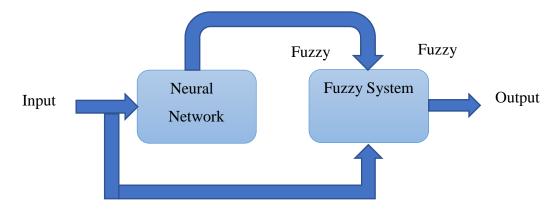

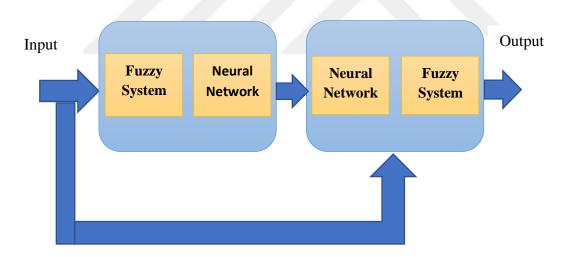

| Figure 3.19. Cooperative Neuro-Fuzzy                                |

| Figure 3.20. Concurrent Neuro-Fuzzy System                          |

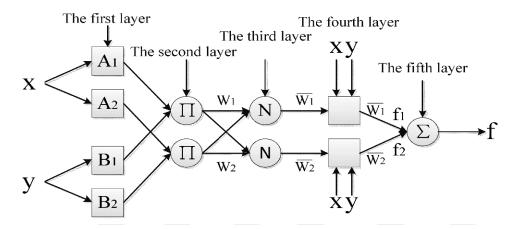

| Figure 3.21. General Structure of ANFIS base on Takagi–Sugeno       |

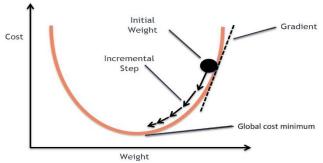

| Figure 4.1. Gradient Descent Optimization                           |

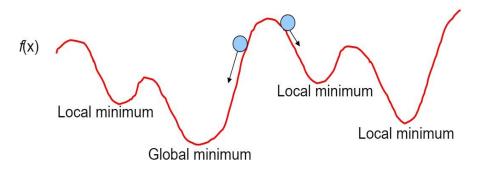

| Figure 4.2. Global and Local Minimum69                              |

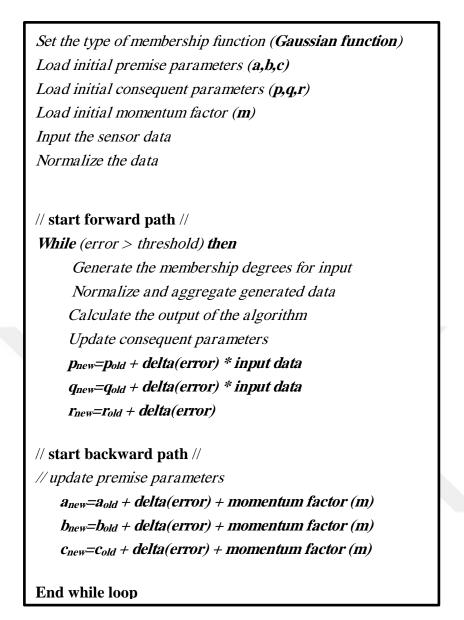

| Figure 4.3. Pseudo Code of the Proposed Algorithm                   |

| Figure 4.4. Training Algorithm based on Handwritten ANFIS71         |

| Figure 4.5. Testing algorithm based on Handwritten                  |

| Figure 4.6. Training Algorithm based on Matlab Toolbox              |

| Figure 4.7. Testing Algorithm based on Matlab Toolbox               |

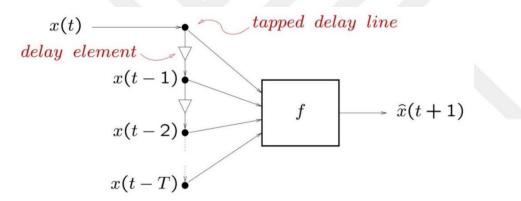

| Figure 4.8. A Standard Structure of Time Series Prediction74                      |

|-----------------------------------------------------------------------------------|

| Figure 4.9. A General ANFIS Algorithm based on Time Series Prediction75           |

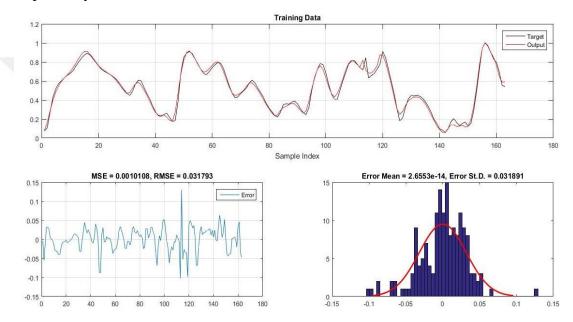

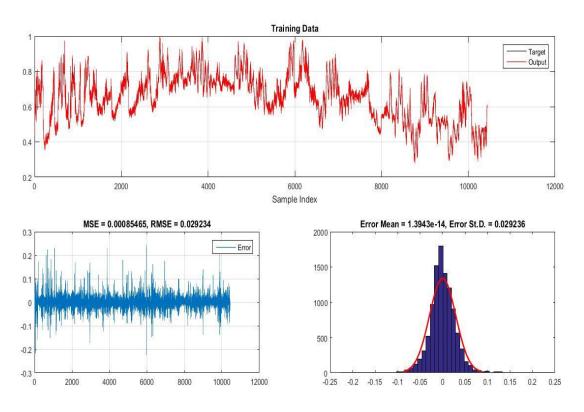

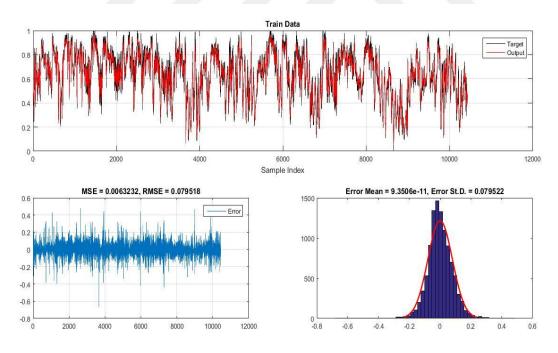

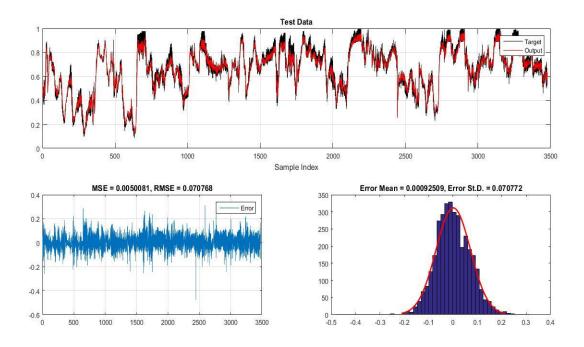

| Figure 4.10. Training of Chicago Park Temperature Set Using Handwritten Algorithm |

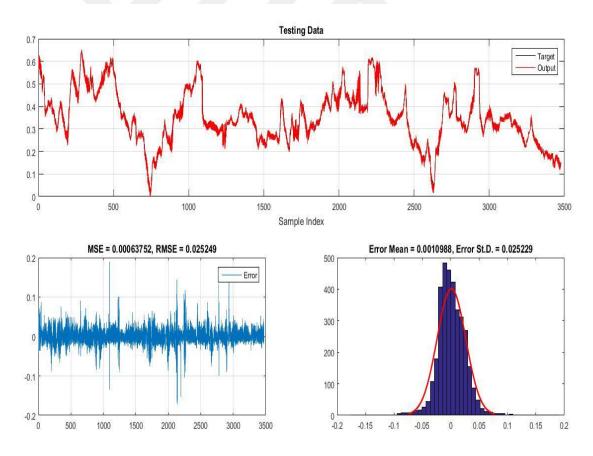

| Figure 4.11. Testing of Chicago Park Temperature Set Using Handwritten Algorithm  |

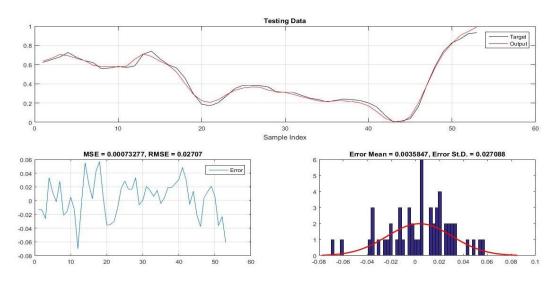

| Figure 4.12. Training of Chicago Park Temperature Set using Matlab77              |

| Figure 4.13. Testing of Chicago Park Temperature Set using Matlab77               |

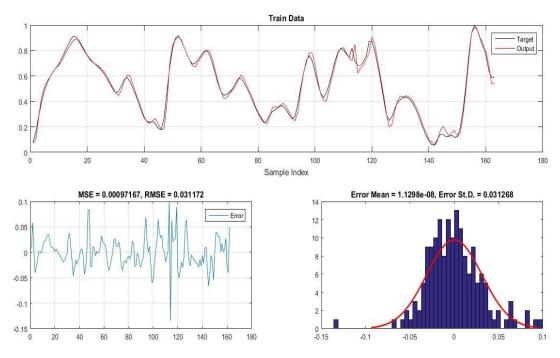

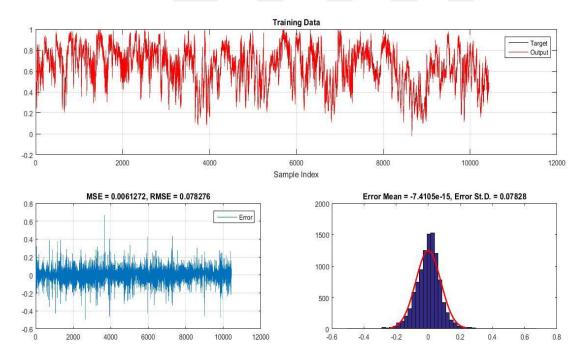

| Figure 4.14. Training of Chicago Park Humidity Set using Handwritten              |

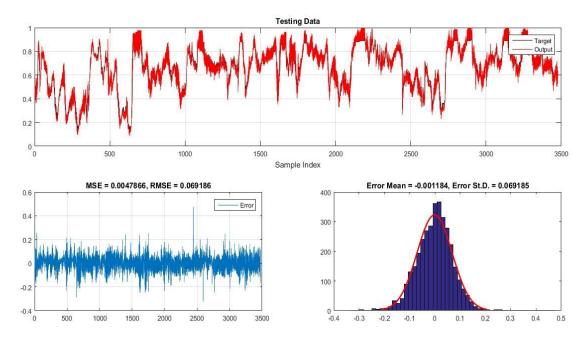

| Figure 4.15. Testing of Chicago Park Humidity Set using Handwritten Algorithm.    |

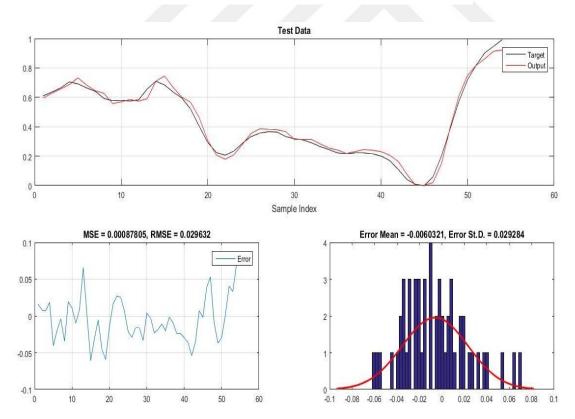

| Figure 4.16. Training of Chicago Park Humidity Set using Matlab Toolbox79         |

| Figure 4.17. Testing Chicago Park Humidity Set using Matlab Toolbox               |

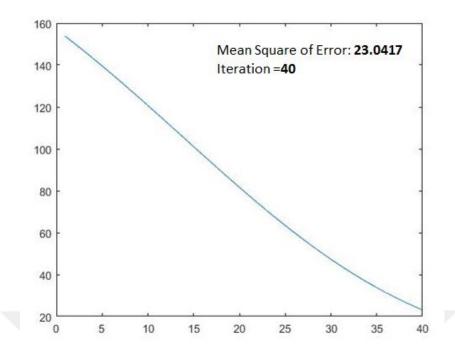

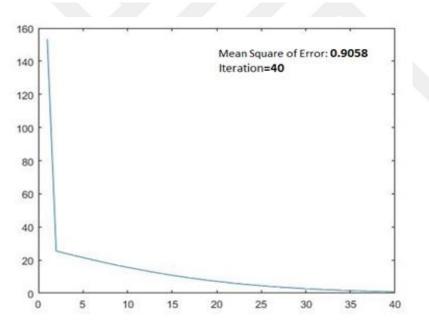

| Figure 4.18. Training Modified Algorithm Without Momentum                         |

| Figure 4.19. Training Modified Algorithm with Momentum                            |

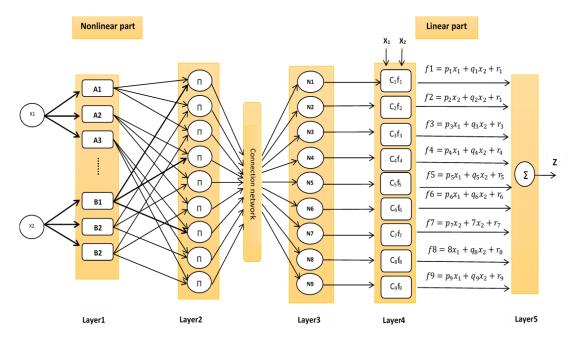

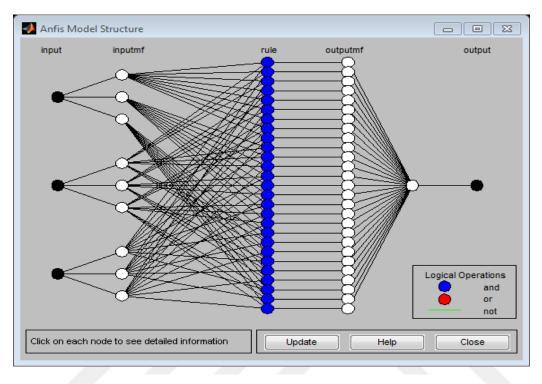

| Figure 4.20. ANFIS Algorithm with 9-Rules                                         |

| Figure 4.21. ANFIS Algorithm with 24-Fuzzy Rule                                   |

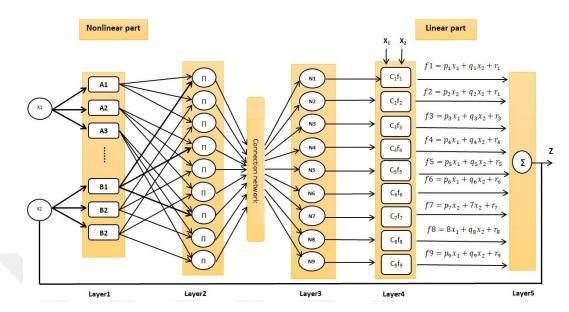

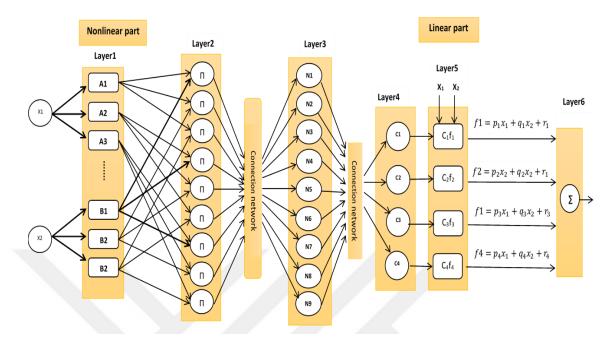

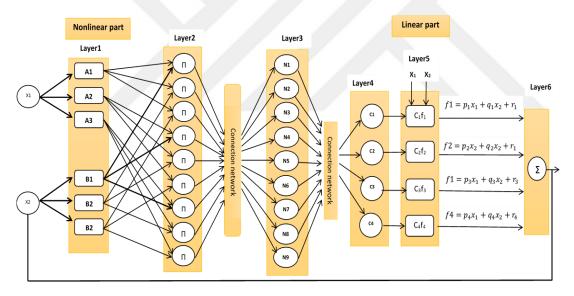

| Figure 4.22. A Modified ANFIS Algorithm with a New Normalization Layer85          |

| Figure 4.23. Extended ANFIS Architecture based on Recurrent                       |

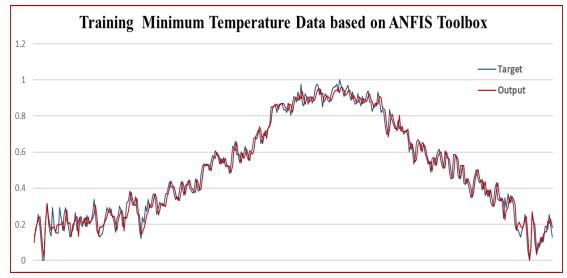

| Figure 4.24. Training Temperature Set using Modified ANFIS and ANFIS Toolbox      |

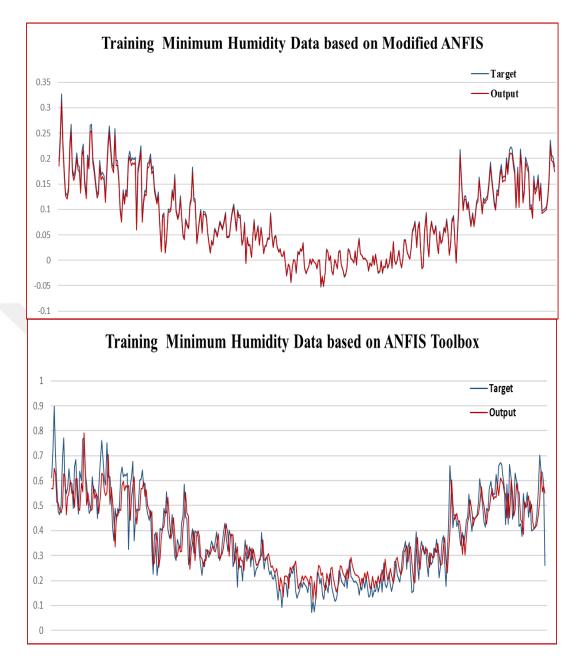

| Figure 4.25. Training Humidity Data using Modified ANFIS and ANFIS Toolbox.       |

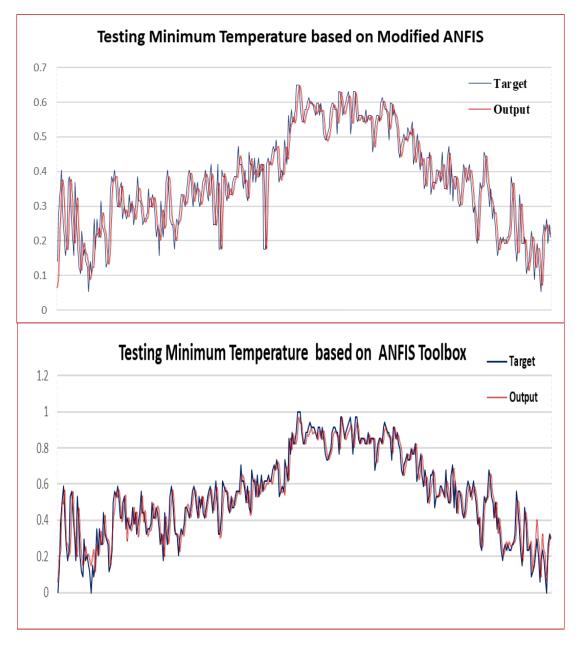

| Figure 4.26. Testing Temperature Data using Modified ANFIS and ANFIS Toolbox      |

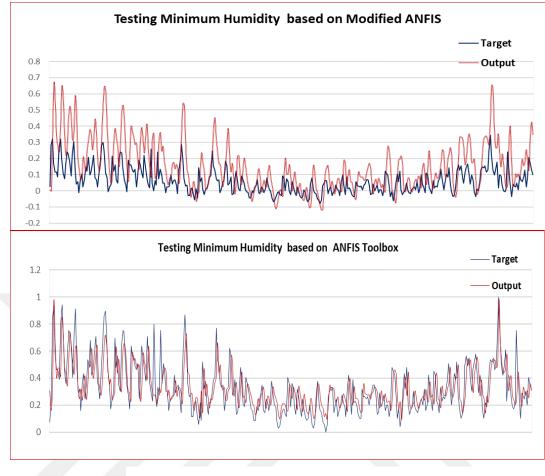

| Figure 4.27. Testing Temperature Data using Modified ANFIS and ANFIS      Toolbox |

|-----------------------------------------------------------------------------------|

| Figure 4.27. Testing Temperature Data using Modified ANFIS and ANFIS Toolbox      |

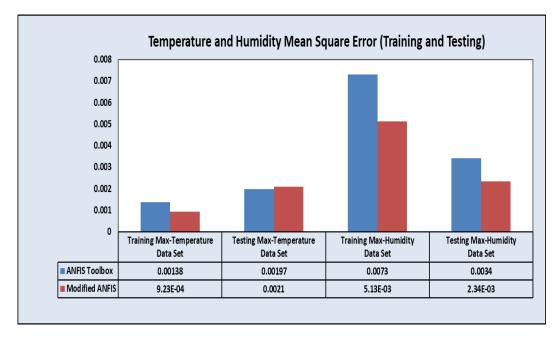

| Figure 4.28. MSE of Training /Testing of Maximum Temperature and Humidity.        |

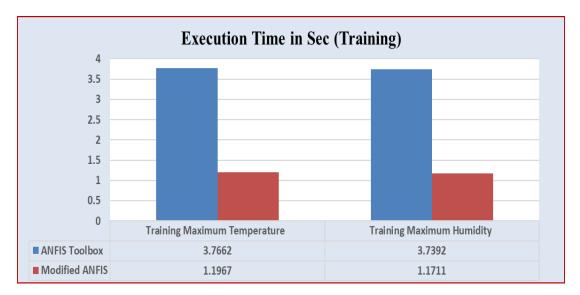

| Figure 4.29. Execution Time of Training Phase                                     |

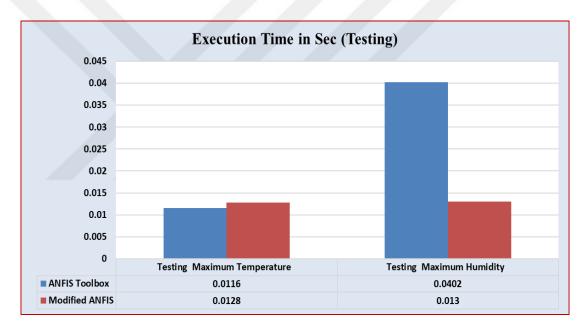

| Figure 4.30. Execution Time of Testing Phase                                      |

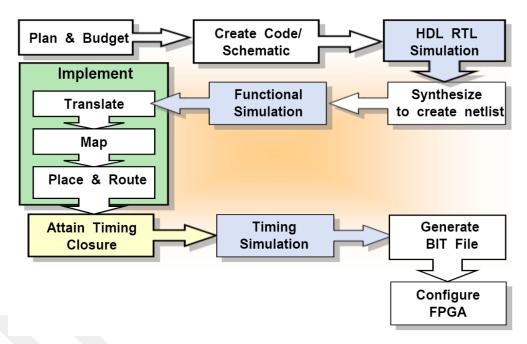

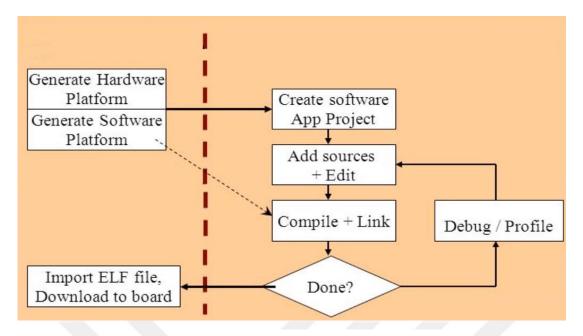

| Figure 5.1. Xilinx Design Flow                                                    |

| Figure 5.2. SDK development Flow                                                  |

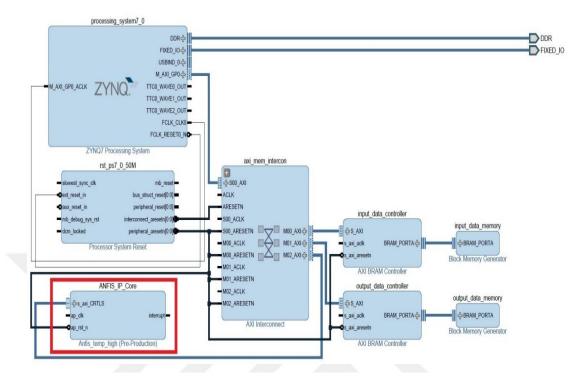

| Figure 5.3. Hardware Design with a Single ANFIS IP                                |

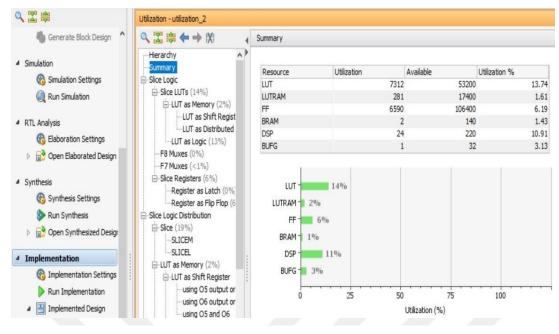

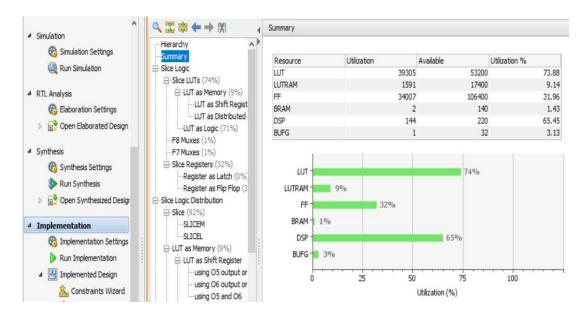

| Figure 5.4. The Utilization Hardware Resources for Single ANFIS IP                |

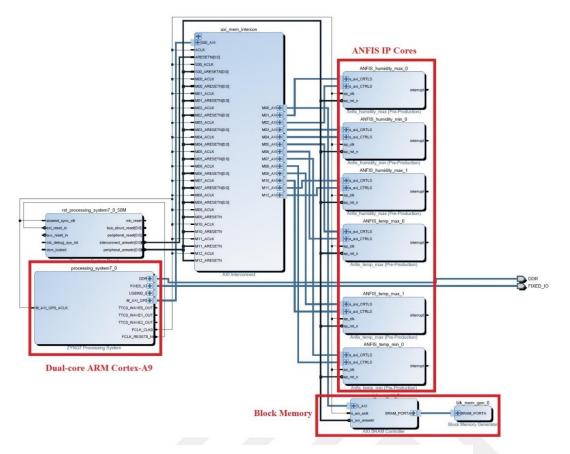

| Figure 5.5. Hardware design with Multi-ANFIS IP core                              |

| Figure 5.6. Hardware Resources for Multi-ANFIS Cores                              |

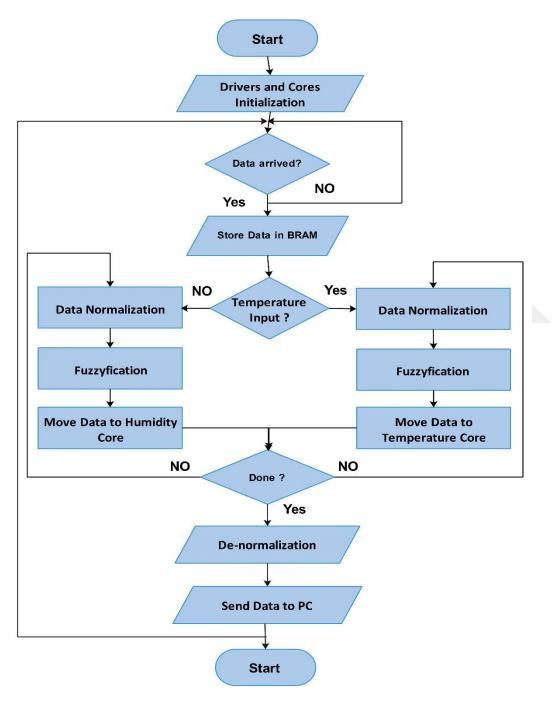

| Figure 5.7. Processing Steps that Implemented by Cortex-a9 Processor              |

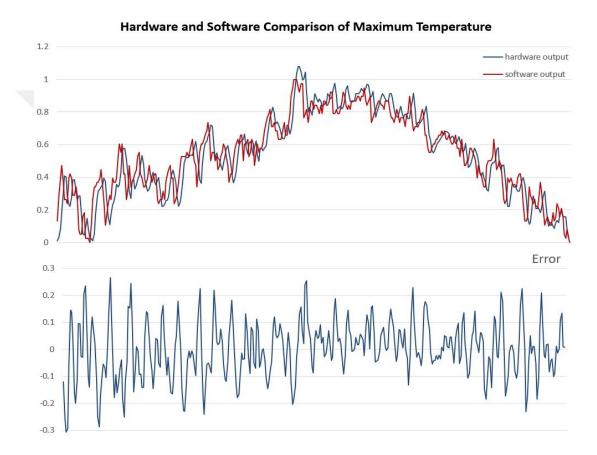

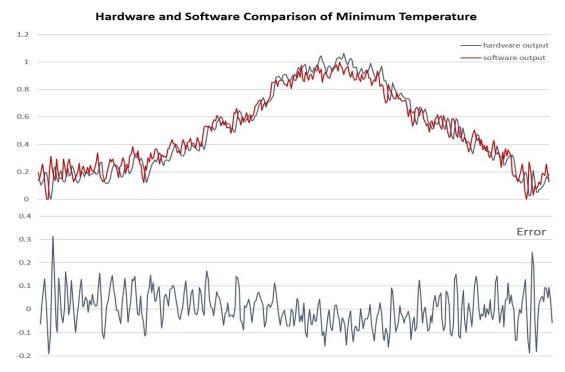

| Figure 5.8. Hardware and Software Comparison of Maximum Temperature 101           |

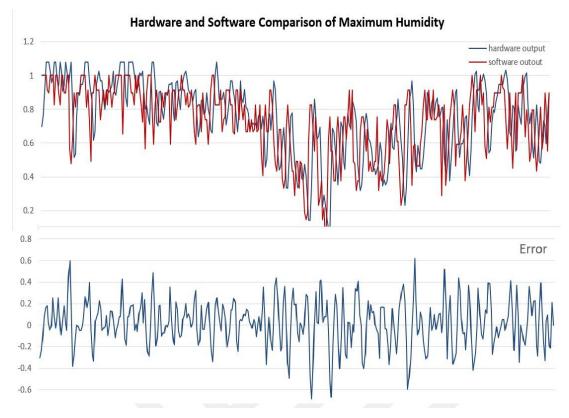

| Figure 5.9. Hardware and Software Comparison of Maximum Humidity 102              |

| Figure 5.10. Hardware and Software Comparison of Minimum Temperature 102          |

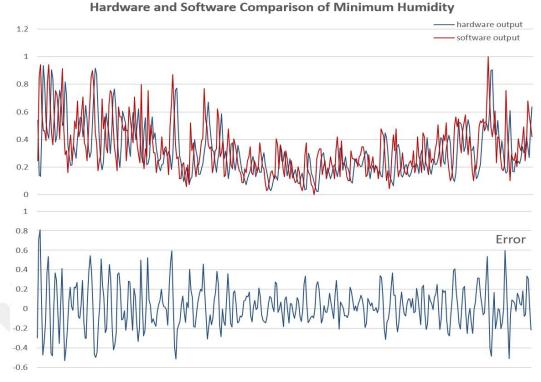

| Figure 5.11. Hardware and Software Comparison of Minimum Humidity 103             |

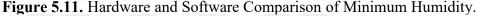

| Figure 6.1. Main parts of Smart Automation System                                 |

| Figure 6.2. Ethernet Message between Multi-function and Aggregation               |

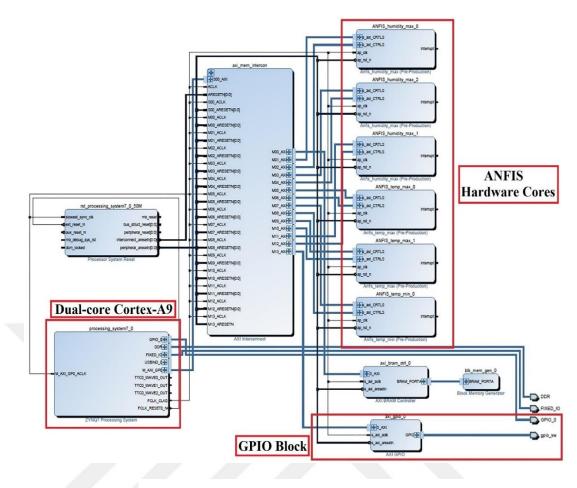

| Figure 6.3. Hardware Design within the Multi-Function                             |

| Figure 6.4. The overall tasks are executed by Cortex-A9                           |

| Figure 6.5. Pseudo Code of the System Actions                                     |

| Figure 6.6. The Interface of the J62 Header                                       |

| Figure 6.7. Initialization of the Lwip Functions                                                       |

|--------------------------------------------------------------------------------------------------------|

| Figure 6.8. handling the system interrupt by lwIP library                                              |

| Figure 6.9. Initialization Structure of the RAW API116                                                 |

| Figure 6.10. Establishing the Connection based on Lwip                                                 |

| Figure 6.11. Data Arrived and Received Callbacks                                                       |

| Figure 6.12. Modified LWIP based on User Datagram Protocol                                             |

| Figure 6.13. Complete Proposed Hardware System                                                         |

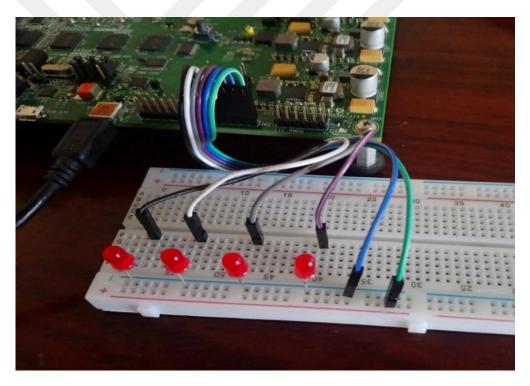

| Figure 6.14. Interfacing Arduino with the Sensors                                                      |

| Figure 6.15. The Connection between Arduino Board and FPGA                                             |

| Figure 6.16. System Graphic User Interface                                                             |

| Figure 6.17. High-level Gas Detector and Temperature/Humidity in the Off-line         State.       122 |

| Figure 6.18. An Example of High-level Detection                                                        |

| Figure A.1. Training Minimum Temperature Data                                                          |

| Figure A.2. Training Minimum Humidity Data set139                                                      |

| Figure A.3. Testing Minimum Temperature Data set                                                       |

| Figure A.4. Testing Minimum Humidity Data Set141                                                       |

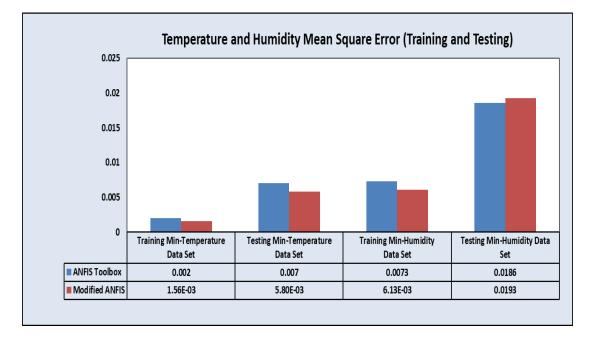

| Figure A.5. MSE of Training and Testing Minimum Temperature and Humidity Sets                          |

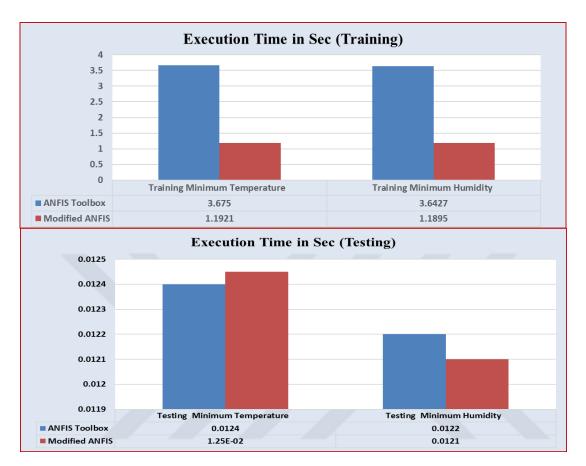

| Figure A.6. Training and Testing Execution Time142                                                     |

### LIST OF TABLES

| <b>Table 2.1.</b> Characteristics of Different FPGA Series of Xilinx                     |

|------------------------------------------------------------------------------------------|

| <b>Table 2.2.</b> Characteristics of Different Altera Series                             |

| Table 2.3. I/O Peripheral Description.    25                                             |

| <b>Table 2.4.</b> PLD as MCU co-processing.    34                                        |

| <b>Table 3.1.</b> Network Selector.    50                                                |

| <b>Table 3.2.</b> Car's driver rules.    53                                              |

| <b>Table 3.3.</b> Example of Air Conditioner Fuzzy Rules.    58                          |

| <b>Table 3.4</b> Example of Fuzzy Rules Matrix.    58                                    |

| <b>Table 3.5.</b> Hybrid Learning Algorithm within ANFIS Algorithm.         67           |

| <b>Table 4.1.</b> Training Results of Global Ice Volume                                  |

| <b>Table 4.2.</b> Testing Results of Global Ice Volume.    73                            |

| <b>Table 4.3</b> . Training and Testing results of Chicago Park Temperature data         |

| <b>Table 4.4.</b> Training and Testing results of Chicago Park Humidity data.         80 |

| <b>Table 4.5.</b> Training Speed (Execution Time) in Sec.    81                          |

| <b>Table 4.6.</b> Testing Speed (Execution Time) in Sec.    81                           |

| <b>Table 5.1.</b> Comparison of Hardware Resources for the Different Approaches97        |

| Table 5.2. Comparison between Hardware and Software versions.         103                |

| Table 6.1. System Actions.    111                                                        |

| Table 6.2. System Fault Alerts.    111                                                   |

### SYMBOLS AND ABBREVIATIONS

- SSR Structure of Scientific Revolution

- NS Normal Science

- EOS Extra Ordinary Science

- ADC Analogue-To-Digital Converter

- ANFIS Adaptive Neuro-Fuzzy Inference System

- ANN Artificial Neural Network

- APSoC All-Programmable System-On-Chip

- APU Application Processing Unit

- ARP Address Resolution Protocol

- ASIC Application-Specific Integrated Circuit

- AXI Advanced eXtensible Interface

- BP Back-Propagation

- CLB Configurable Logic Block

- COA Centroid of Area

- COS Center of Sums technique

- DAC Digital-To-Analogue Converter

- DHCP Dynamic Host Configuration Protocol

- DSP Digital Signal Processing block

- EEPROM Electrically Erasable Programmable Read-Only Memory

- EMIO Extended Multiplexed Input / Output

- ESL Electronic System Level

- FF Flip-Flop

- FFT Fast Fourier Transform

- FIFO First In First Out

- FIR Finite Impulse Response filter

- FLS Fuzzy Logic System

- FPGA Field Programmable Gate Array

- GDM Gradient Descent

- GEM Gigabit Ethernet Controllers

- GPIO General-Purpose Input /Output

- GUI Graphical User Interface

- HAS Home Automation System

- HDL Hardware Description Language

- HLS Vivado High-Level Synthesis

- IC Integrated Circuit

- ICAP Internal Configuration Access Port

- ICMP Internet Control Message Protocol

- IDE Integrated Design Environment

- IGMP Internet Group Message Protocol

- IOBs Input/output blocks

- IP Intellectual Property

- IP Internet Protocol

- iPSO improved Particle Swarm Optimization

- IT Information Technology

- LSM Linear Least Squares Algorithm

- LUT Look-Up Table

- lwIP Light weight IP

- MAC Media Access Control

- MF Membership Function

- MIO Multiplexed Input / Output

- MOM Mean of Maxima Technique

| MSE  | Mean Squared Error                            |

|------|-----------------------------------------------|

| NFS  | Neuro-Fuzzy System                            |

| PC   | Personal Computer                             |

| PL   | Programmable Logic                            |

| PLD  | Programmable Logic Devices                    |

| PS   | Processing System                             |

| RAM  | Random Access Memory                          |

| RMSE | Root-Mean-Square Error                        |

| RNN  | Recurrent Neural Network                      |

| ROM  | Read Only Memory                              |

| RTL  | Register Transfer Level                       |

| SDK  | Software Development Kit                      |

| SDK  | Xilinx Software Development Kit               |

| SIMD | Single Instruction Multiple Data              |

| SoC  | System-on-Chip                                |

| SRAM | Static Random-Access Memory                   |

| STD  | Standard Deviation                            |

| ТСР  | Transmission Control Protocol                 |

| UDP  | User Datagram Protocol                        |

| VHDL | Very high-speed Hardware Description Language |

| WSN  | Wireless Sensor Network                       |

# CHAPTER 1 INTRODUCTION

A wireless sensor network (WSN) is a collection of specialized sensor nodes that are connected with a specific communications protocols for observing and recording physical parameters at different locations and then, forward the collected data to the end user. Temperature, humidity, sound intensity, speed, pollutants, wind direction, light, and pressure are examples of the common monitored conditions. Wireless sensor networks provide precise information according to the requirements of the user. Therefore, they enable a huge number of applications such as industrial control systems, health-care, and target tracking in military fields, weather monitoring systems, and home automation systems.

There are many advantages of wireless sensor networks over conventional sensing systems. Because WSNs are deployed in vast scale, they provide more precise data about monitoring objects. In addition, these network systems are also easier to establish and more scalable when compared with traditional wired systems.

Wireless sensor networks have many unique attributes stated in these references (Sohraby, Minoli, and Znati, 2007; Karl and Willig, 2007; Ilyas and Mahgoub, 2004):

- Size: In real applications, the size of sensor nodes is small to reduce the sensor deployment cost.

- Power: The power of Wireless sensor network nodes has a limited energy constraint. However, most utilized applications follow different operating conditions of sensor nodes to maintain the battery power for a long time.

- The large scale of deployment: Large scale of deployment increases the observation accuracy and reduces the communication distance between nodes. This also improves communication quality and increases energy efficiency. A large number of sensor nodes is also a prime enabler for robust communication in mesh wireless sensor network.

- Mobility: Environmental impacts on sensor nodes such as wind or rain, may change their initial position deployment. On the other hand, they can change their position according to the demand for the system properties.

- Unattended operation: Because a huge number of devices are distributed in a WSN, unattended operation and failure-tolerance of every sensor node becomes an essential necessity.

- Low Cost: Since sensor nodes are distributed in wide-range, the cost of a single sensor node is the influential factor in the overall cost of different applications of WSN's. Furthermore, most applications of the wireless sensor network in civilian fields are named price-enabled applications. That means the markets wait for competitive prices to utilize the application.

- Heterogeneity: In general, wireless sensor networks may be composed of various types of nodes. The computational power of some types of sensor nodes may be more than others; the degree of heterogeneity within a WSN has an impact on the complexity and management method of the overall system.

The energy budget limitations of these platforms have led to constructing a very low power system that can perform complex functions with minimum resources utilization. Not only the technology of wireless sensor networks has attracted much interest, but also the ability to implement it in several fields such as agriculture, military, tracking system, biomedicine, etc. Because WSN's have become a universal subject, most of the engineering can discover an advantage or offer a new contribution.

In general, simple and traditional microcontrollers that are used within sensor nodes are not suitable efficiently to handle complex tasks for data processing. To achieve high-performance computing, multi-processor systems are becoming compulsory. However, these kinds of systems do not suitable for low power consumption platforms such as WSNs. The integration of application-specific hardware accelerators with sensor nodes plays a key role to reduce the overall power consumption.

The energy and required time that is used for data processing tasks when implementing them with specific digital logic can be minimized to several times compared to software solutions. Furthermore, the wide range of WSN applications means that a high level of flexibility can be achieved in the underlying hardware. Consequently, a single infrastructure system can be re-utilized for several purposes.

Modern improvements in the of Programmable Logic Devices (PLD) design Have a significant impact on the rate of energy consumption of these chips, which can be used to reconfigure the digital circuit to implement complex tasks of data processing. So, the process of reducing power consumption (static and dynamic power) by integrating it with high logic intensity makes these kinds of logic devices a preferable choice for flexible hardware acceleration. Reconfigurable hardware appears then as a possible solution to provide an adequate level of computation power for any sensor node while providing additional hardware resources for the implementation of different applications in several domains.

#### 1.1. Research Scope and Objectives

In this thesis, we discuss the possibility of integrating FPGA Device in the architecture of sensor nodes. The employment of re-programmable hardware architecture is discussed at multiple levels of abstractions, start from the selection of technology up to employ it in real-world applications and the modification of suitable software programs. In addition, this thesis covers multiple subjects such as architecture design of embedded systems, reconfigurable technologies, and some of the soft computing technologies such as neural network algorithms, fuzzy control systems, and neuro-fuzzy structures. In general, our thesis answers the following questions:

- What are the benefits and structures of sensor nodes using reconfigurable hardware acceleration? To answer this question, we need to identify the current structure of the sensor node and potential improvements. The effect of reconfigurable acceleration on the sensor node will be discussed and three types of sensor nodes depend on reconfigurable hardware acceleration are presented.

- How to combine reconfigurable devices with the structure of sensor nodes and keep the level of power consumption minimum? To solve this problem, three techniques are implemented to define appropriate structure where total overhead stays unimportant. This structure will be confirmed by designing a hardware model performing typical functions of a sensor node.

• What kind of soft computing technology that is suitable for the applications of sensor nodes? What kind of software tools are used to implement it within the sensor node? In this thesis, different approaches of soft computing techniques are presented with the pros and cons of each approach. On the other hand, the abundance of WSN's applications leads to a variety of programming methods where the components of the software and hardware system can be rapidly used for sensor node. So, several tools are utilized to create the sensor node based on programmable devices. As a result, we will introduce a new generic smart sensor node that can be customized for any kind of data processing algorithms. This integration approach provides high flexibility, which can permit the implementation of a wide range of processing tasks. This flexibility can be obtained by supporting dynamic reprogramming which means the function of the sensor node can be replaced at any time.

#### **1.2.** Thesis Outline

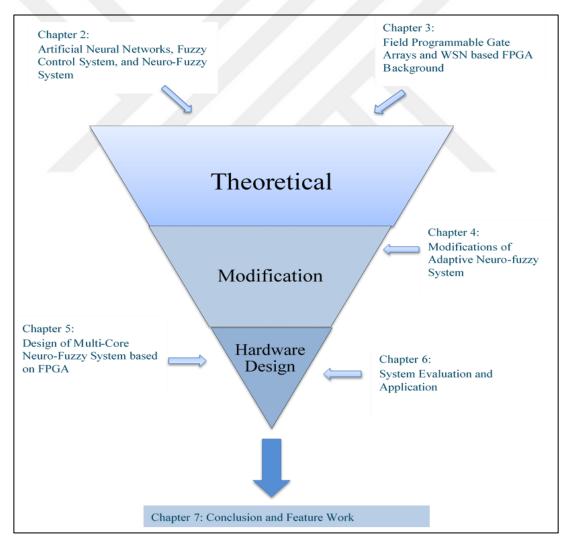

This thesis is divided into four principal parts. In Part I, the thesis' background and motivation are described, the theoretical of soft computing (artificial neural networks, fuzzy control system, and neuro-fuzzy system) and field programmable gate array that related with this thesis are introduced in Part II. In Part III, we will discuss the proposed modification of neuro-fuzzy algorithm and variety of hardware connotations and tools that are used to design reconfigurable device on a sensor node. The evaluation and the application of the proposed sensor node is presented in Part V. **Figure 1.1** demonstrates the general organization of the thesis. The sections below, introduce a brief outline of the chapters that comprising these four different parts:

#### Part I: Chapter 1:

- The background, advantages, and Challenges of wireless sensor networks.

- The Research Scope and Objective.

- Literature review of some related works.

#### Part II: Chapter 2 and Chapter 3:

- Theoretical of neural networks, fuzzy control system, and neuro-fuzzy system

- Theoretical of Field Programmable Gate Array devices

#### Part III: Chapter 4:

• Modifications of Adaptive Neuro-fuzzy System

#### Part III: Chapter 5 and Chapter 6:

- Hardware concepts

- Tools that are used to design of reconfigurable device

- Design of Multi-Core Neuro-Fuzzy System based on FPGA

- System Evaluation and Application

#### Part V: Chapter 7:

• Sums up our thesis by summarizing the main contributions and suggesting outlines for future work.

Figure 1.1. Outline of the Thesis.

#### **1.3. Existing Studies**

Field Programmable Gate Arrays include reconfigurable logic elements called Logic Blocks, and smart programmable interconnects that permit these blocks to be wired together. By employing Hardware Description Languages (HDLs) like Verilog or VHDL, designers can configure these reconfigurable blocks to achieve complex logic structures. Several pre-designed FPGA generic component cores exist which permit implementing multipliers, processors, network protocols, etc. So, FPGA devices are extremely flexible especially when they come to designing complex systems.

FPGA technology is being used in several application fields such as telecommunications(Khedkar and Khade, 2017; Yonezawa et al., 2017), signal and image processing(Bhattacharyya, Deprettere, Leupers, and Takala, 2018; Li, Xu, and Zhang, 2017; Sarpotdar, Mathew, Safonova, and Murthy, 2016; Woods, McAllister, Lightbody, and Yi, 2017), automotive applications, robotics(Poudel, Giri, and Munir, 2017; Sahlbach, Thiele, and Ernst, 2017; Velez and Otaegui, 2016), space landing crafts(Guinn et al., 2016; Schrader, Bredemeyer, Mihalachi, Rohde, and Kleine-Ostmann, 2016; Yang et al., 2016).

With the advancements of using reconfigurable FPGA and soft computing techniques, many studies have been done in this field. Cihan, Fuat, and Mehmet in (Karakuzu, Karakaya, and Çavuşlu, 2016) show the ability of implement the meta-heuristic learning algorithms of the neuro-fuzzy system (NFS) on the FPGA based on improved particle swarm optimization (iPSO). According to the authors, this implementation does not need any memory and multiplier usage. Gaussian MF is used as the main membership function. This kind of function has an exponential operation and cannot be realized directly within FPGA. So, the authors proposed a kind of function approximation in order to reduce the number of required hardware resources. The proposed approximation function requires one multiplier, one divider, and three adder modules. Results indicate that proposed implementation and membership function approximation is more effective than other approaches and requires less FPGA hardware resources.

Another parallel implementation of digital ANFIS algorithm using FPGA Zynq processor with single and dual based on VHDL (Very high-speed Hardware Description Language) language was presented in (Darvill, Tisan, and Cirstea, 2017).

Using HDL approach provide fast prototyping and allowing powerful synthesis utilization. Comparison between parallel and serial methodology was done in this article. The authors show that there are many advantages of using parallel architecture over existing serial methodology such as clock cycles and logic utilization in addition to reducing the number of redundant calculation cycles that provide higher scalability compared with the serial approach. Another parallel hardware implementation of ANFIS algorithm was done in (Nadu & Nadu, 2017).

Implementing ANFIS algorithms for real-time control applications is the main challenge. The difficulties come from real-time linear and nonlinear parameters and the adaptation of the control systems (Tămas and Brassai, 2015). Distributing the functions of ANFIS algorithm between multiple dedicated hardware modules work together in parallel can solve these challenges. In other words, the ANFIS IP (Intellectual Property) controller is used to run the main function of the algorithm and the ARM hard-processor in Zynx FPGA kit is used to adapt and train all ANFIS parameters.

Other studies use dual-core hard-processor and a programmable logic part based on Vivado High-Level Synthesis tool with high-level language like C/C++. Parallel ANFIS architecture uses a very high processing speed and the parameter adaptation works in parallel with the output processing in real-time can be found in (Tămas and Brassai, 2015).

The authors in (Łapa, Zalasiński, and Cpałka, 2013) present a new methodology based on an evolutionary strategy for nonlinear modeling in order to perform the reduction of complexity in neuro-fuzzy systems and adapt the parameters and the selection of simple rules for the system structure. This work enhances the operation of ANFIS algorithm and reduces computational tasks and its complexity. There are some other works tried to reduce the data dimensions and the complexity of the neuro-fuzzy systems by combining them with other soft computational methods such as particle swarm optimization (Ghasemi, Kalhori, & Bagherpour, 2016; Rini, Shamsuddin, and Yuhaniz, 2016) or with data mining algorithms like C-means (Çavdar, 2016; Kaur, Dhar, and Guha, 2016).

Authors in (C. Chen, John, Twycross, and Garibaldi, 2016) extend the traditional five layers architecture of the ANFIS algorithm to a 6-layer architecture that allows the

fuzzification and the node at the inputs layer to be more explicit. The first layer in the extended architecture has been divided into two layers (layer 0 and 1). The first layer (layer 0) is a fuzzification layer, which is used to generate membership grades of all crisp inputs while the layer 1 calculates the largest membership grade for layer 0 nodes.

According to the existing and reachable literature, we decided that the overall thesis design can be covered up into two folds. The first fold deals with improving the performance of ANFIS algorithm by combining it with other soft algorithms or trying to modify and extend its architecture. The other fold attempts to implement the ANFIS in reconfigurable FPGA based on different methodologies. Our contribution aims to integrate these two folds by extending the architecture of the ANFIS algorithm and using the FPGA to implement the algorithms for real time systems.

On the other hand, several studies use the FPGA for real-time smart home automation systems. In the study of Mohd and Mamun in (Marufuzzaman, Bin, Reaz, & Islam, 2014). authors propose a methodology based smart algorithm for recognizing and analyzing activities of daily life based on FPGA. The modified algorithm aims to classify the home events based on intelligent multi-agent algorithms that interact with each other. The system consists of four prediction agents (event, time, location, power) and one agent for decision-making. Based on the inferential processes within the prediction agents, they forward the necessary commands to the Decision-Making Agent.

Other FPGA prototype of a home automation system based on Artificial Intelligent can be found in (M.B.I. Reaz, Assim, Choong, Hussain, & Mohd-Yasin, 2006). The authors design a system that includes three main units: the prediction unit, the decision unit, and the communication unit. Active-Lezi algorithm for the online predictor is used in the prediction unit to predict possible future actions. While the Q-Learning algorithm that is a kind of reinforcement learning technique is used within the decision unit in order to make the final system decision. Other similar FPGA implementation based artificial intelligent for home automation can be found in (Mamun Bin Ibne Reaz, 2013).

The authors in (Sang-hyun, Lee, and Kyung-il, 2013) propose the methodology that integrates ANFIS with the smart home system to eliminate the difficulties that face the sensors in traditional home systems and generate the intelligent and adaptive system.

The authors design multiple ANFIS algorithms in order to take multiple dynamic decisions. Multiple ANFIS have the ability to deal with the nonlinear and complex events system; as a result, the high efficiency can be achieved in the Home Automation System (HAS).

Another implementation based on FPGA, embedded systems, and web technologies is proposed in (Rusu and Duka, 2017). The proposed system has the ability to control and manage multiple house systems through the internet using a single internet page. According to the authors, the system has many advantages over the similar FPGA implementations like the ability to monitor and control more than one home system through a single web page and LCD panel at the same time. The system has also the flexibility to support different types of communication protocols. Finally, the hardware system is very fast because of the response time between the FPGA kit and the web page is about 500 milliseconds.

To the best of our knowledge, there are some other studies using different wireless communication technologies for FPGA connectivity and HAS. Examples are in the references (Suresh and Mastani, 2018; P Waghmare, Chaure, Chandgude, and Chaudhari, 2017) for Bluetooth communication and (Asadullah and Raza, 2016; Gaikwad, Gabhane, and Golait, 2015; Panigrahi, Qureshi, Saxena, and Reddy, 2016; Sharma et al., 2015) for Wi-Fi in addition to previously used wired technologies.

## CHAPTER 2 FIELD PROGRAMMABLE GATE ARRAYS

#### 2.1. Introduction

FPGAs are devices in which almost any digital circuit can be implemented just by using programming languages such as Hardware Description Language or by Schematic Capture. They are used in electronic fields to build complex sequential or combinational logic circuits in order to reduce space and to avoid Application specific ICs design cost. In this chapter, we will give an introduction about the internal structure of this device and how can be used to build a new generation of WSNs.

#### 2.2. Field Programmable Gate Array Structure

Field Programmable Gate Array (FPGA) is a device which consists of a huge number of reconfigurable logic circuits and gives particular reprogrammable circuit. When an FPGA is programmed, the internal logic circuits are connected in a way that allows producing a specific hardware achievement of a software application. In general, FPGA devices do not have any operating systems and they utilize dedicated hardware resources for a specific processing application. Because of the parallel nature of FPGA devices, they do not need to compute the same hardware resources for multiple software applications. So, the performances of fabric FPGA parts of the different applications are not affected in case of much additional processing are added. In addition to a single FPGA device can run multiple control loops at multiple rates and this is one of the main distinctions between the FPGA devices and general processors.

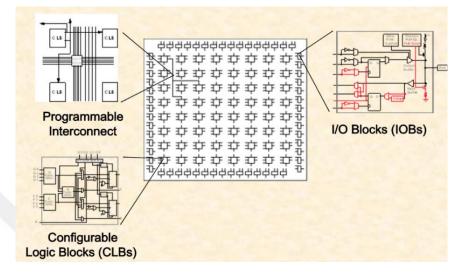

A single FPGA has millions of digital logic circuits and can be used instead of thousands of analog components by incorporating in one integrated circuit (IC). The flexibility of the general structure of the reconfigurable FPGA is explained in Figure 2.1. The FPGA comprises three main reconfigurable parts: Configurable Logic Block (CLB), Programmable Interconnects, and Input/output blocks (IOBs). All these parts

can be reconfigured to implement complex applications. reconfigurable IOBs represent as a ring around the FPGA microchip and provide access to the I/O FPGA package pins. While the CLBs distributed as a rectangular behind the IOB(D. Chen, Cong, & Pan, 2006)(Lee & Seshia, 2011).

Figure 2.1. General Structure of Reconfigurable FPGA

The Configurable Logic Block of an FPGA can be programmed to implement various kind of combinational functions, sequential functions, or combinations of both of them in a simple way. CLB can be configured by one of these methods(Bobda, 2008):

- 1. Combinational logic circuits such as AND, OR, XOR, NAND, etc.

- 2. Lookup tables

- 3. Multiplexers and De-multiplexers

- 4. And-OR structure.

- 5. Transistor pairs

Routing process in FPGAs between CLB is done by programmable interconnects that consists of a various length of wire that can perform the interconnection through configurable switches. The density of CLB that is used for specific application within FPGA is based on length and number of programmable wires applied for the routing process. Simplified routing in internal FPGA architecture is shown in Figure 2.2.

Figure 2.2. Simplified Routing in FPGA Architecture

#### 2.3. FPGA Programming Technologies

There are many technologies of programming FPGA devices that have been used to configure internal architectures. Each technique has different characteristics which have a major effect on the reconfigurable architecture. Some of the techniques comprise SRAM (Static Random-Access Memory), EEPROM (Electrically Erasable Programmable Read-Only Memory), and Anti-fuse(Maxfield, 2004).

#### 2.3.1. FPGA Based SRAM

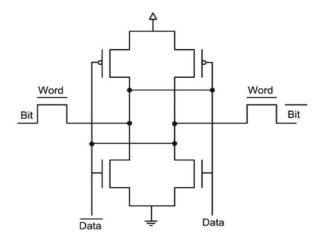

Static memory cells are the essential elements that are used for FPGAs. Most commercial vendors use static memory (SRAM) based programming technology in their devices. SRAM cells in general, are applied to configure the internal routing of FPGAs which are normally drive by digital multiplexors and to re-configure the CLBs within FPGA devices which are used to perform the various logic functions. Figure 2.3 is an example of a static memory cell that is used in re-configurable devices. In this picture, SRAM stores a bit of data on four transistors using two cross-coupled inverters. The two stable states characterize 0 and 1. During read and write operations another two access transistors are used to manage the availability to a memory cell.

Figure 2.3. Static Memory Cell

Because SRAM-based technology uses the CMOS technology, it becomes a prevalent approach that is used in FPGAs. Also, it improves integration, speed and decreases the power. Using the SRAM technology-based FPGA can be infinitely re-configurable and soldered into the hardware board. The implemented function can be changed very quickly in the field by modifying the information that is stored in the PROM or upload a new application code. But this process takes a huge number of digital look-up table (LUT). Also, the FPGA-based this technique needs to re-program the device every time when the power is turned on.

#### 2.3.2. FPGA Based Anti-fuse

Another alternative to Static memory cells is anti-fuse technology. A high-density interconnect is one of the most important characteristics of this programming technology. This programming technology has a huge number of internal interconnections and that makes the logic application small and efficient. So, the placing and the routing process is much easier and doesn't take a long time. Also, the resistance and capacitance are small when compared with other programming technologies.

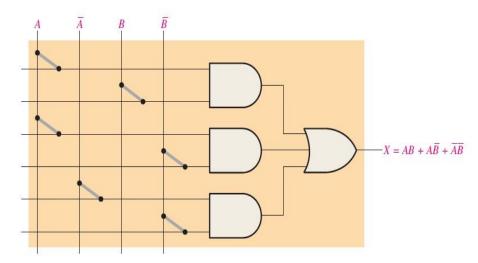

But these kinds of devices are one-time programmable, and we cannot make any change in its design. Another disadvantage of this technology is the demand to integrate all cells of the anti-fuse structure within the integrated circuit (IC). Figure 2.4 demonstrates an example of an array of AND/OR gates connection with two inputs and one output based on anti-fuse technology.

Figure 2.4. AND/OR Structure Based on Antifuse

#### 2.3.3. EEPROM Based

One of the most commonly used and more efficient technologies is the |FPGA based EEPROM cells. This type can be used for two purposes, as s control device like static memory cell or it can be used as a very efficient re-configurable direct switch.

These devices are non-volatile when compared with the SRAM, so they don't lose its content when power off and do not need any additional PROM for booting. But the process of the EEPROM is more complex and has finite number of re-configurable times when compared with SRAM technology.

#### 2.4. Advantages of using an FPGA

There are many advantages of utilizing FPGA devices over using Application-Specific Integrated Circuit (ASIC) like microcontrollers. The FPGAs are very flexible, reusable, and faster to obtain. Usually, FPGAs are more expensive and have a lower value of production than an ASIC or microprocessor. On the other hand, an FPGA is very cost efficient because of the ability to reprogramming unlimited time for different application tasks. The performance of FPGA is very high because of the parallelized technique that uses in internal architecture. Also, we can build many soft or hard microcontroller inside one FPGA package. Another facility in FPGA is that the ability to re-configurable a portion of its internal fabric while other portions are still working. Any new modification future in the final design can be modified by generating and downloading a new bit-stream file. In the FPGA environment, the user doesn't need to know every hardware details. The software will carry out everything such as routing and placement. Also, the timing constraint will be done automatically to fit the design specifications. After the design is completed and downloaded it as a bit-stream file, the FPGA will convert to a kind of ASIC (D. Chen et al., 2006; D. Chen et al., 2006 ;D. Chen et al., 2006).

# 2.5. FPGAs Employed

The Xilinx and Altera are the most common manufacturers in the market which provide the FPGA devices. Other several manufacturers can also provide FPGAs such as Semiconductor, Atmel, etc.

### 2.5.1. Xilinx:

Xilinx is an American company and it is one of the first and important fieldprogrammable gate array (FPGA) providers. The Virtex and Spartan series are the two families that supplied by this company and they are widely utilized in the market. There are many differences between those two families related to cost and performance.

## 2.5.1.1. The Spartan series of FPGAs

The Spartan family is designed primarily for the low cost and simple solutions that don't need a high performance such as the routing algorithms that are used in the wireless sensor networks. Below some of the famous Xilinx Spartan series (Capability, 2016; June and Ram, 2013; Xilinx, 2011):

- The Spartan-6 family is mostly used by sensor designers for wireless communications or for the automotive applications as a lower cost solution and minimum energy consumption.

- The Spartan®-3AN family is a nonvolatile technology that combines between the attributes of previous Spartan-3A family and system-based flash memory technology for programming and data storage.

• The Spartan-3 family is normally utilized to perform real-time applications combined with fuzzy system controller and other applications that need large number of I/O ports.

### 2.5.1.2. The Virtex series of FPGAs

The Virtex series are utilized as a solution for the highest system performance (Xilinx Inc., 2013). Many features are integrated with this series compared with the Spartan series which include Ethernet MAC blocks (Media Access Control), Digital Signal Processing block (DSP), FIFO logic, high-speed transceivers, and PCI-Express controllers. In addition, the Virtex series have many fixed hardware functions that embedded internally and commonly used such as memories, hard cores of microprocessors, serial transceivers, etc.

- The Virtex 7 series is intended to achieve a high-performance at 50% lower power when compared to the Virtex-6 generation devices. Also, memory bandwidth in Virtex-7 is doubled compared to previous Virtex FPGAs generation(Xilinx Inc., 2013).

- The designers of sensor systems try to use the Virtex devices like Virtex-7 or previous generation such as Virtex-II, Virtex-II Pro, etc. in order to implement the complex functions within the sensing systems specifically in wireless sensor networks (WSN) because the FPGA devices are a powerful and robust and a highperformance devices at an acceptable cost.

Table 2.1 shows the characteristics of the different FPGA series of Xilinx.

| Family        | Process (nm) | LUT Size | Logic Cells  | RAM (bits)  | Number of<br>DSP Blocks | HC-Processor  |

|---------------|--------------|----------|--------------|-------------|-------------------------|---------------|

| Spartan-II    | 180          | 4        | 432–5.3 k    | 16 K–56 K   | -                       | -             |

| Spartan-III   | 90           | 4        | 1.5 k–66 k   | 72 k–1.8 M  | 4-104                   |               |

| Spartan-6     | 45           | 6        | 2 k–147 k    | 144 K–4.8 M | 4-180                   | -             |

| Artix-7       | 28           | 6        | 11 k–215 k   | 720 K-13 M  | 40-740                  | -             |

| Kintex-7      | 28           | 6        | 19 k–477 k   | 2.3 M-34 M  | 120-1920                | -             |

| Virtex        | 220          | 4        | 1.7 k–27 k   | 32 K–128 K  | -                       | -             |

| Virtex-E      | 180          | 4        | 1.7 k–73 k   | 65 K–851 K  | -                       | . <del></del> |

| Virtex_II     | 120/150      | 4        | 512–93 k     | 72 K–128 K  | 4-168                   | -             |

| Virtex-II Pro | 90/130       | 4        | 2.8 k-88 k   | 216 K-7.8 M | 12-444                  | PowerPC 405   |

| Virtex-4      | 90           | 4        | 12 k–200 k   | 648 K–9.7 M | 32-96                   | PowerPC 405   |

| Virtex-5      | 65           | 6        | 12 k–415 k   | 936 K–18 M  | 32-1056                 | PowerPC 405   |

| Virtex-6      | 40           | 6        | 46 k–474 k   | 5.5 M-37 M  | 288-2016                | -             |

| Virtex-7      | 28           | 6        | 179 k–1954 k | 14 M-68 M   | 700-3600                |               |

Table 2.1. Characteristics of Different FPGA Series of Xilinx.

# 2.5.2. Altera

Altera is also an American manufacturer that provides programmable logic devices (PLDs) and different types of reconfigurable circuits. Three main families of FPGA devices are provided by Altera: the low-cost Cyclone series, the mid-range Arria series and the last one is the Stratix series that is used for applications that need high-performance. The interesting thing is that all these families are focusing on its soft-core processors that is called NIOS processor series within its FPGA logic devices instead of hard-core processors compared with Xilinx families.

- The Cyclone series: This series was designed for applications that required lowperformance and low-cost. It is well suited for many sensor applications such as acquisition real data, hardware image processing, and IR Sensors based Signal Conditioning Circuit. The FPGA Cyclone VI is the recent series from Altera that has 4-input LUT in addition to a register which is associated on the output (Cyclone and Partners, 2003).

- In Stratix FPGAs: They have a similar architecture that is found in the Cyclone series with additional improvements. The LUT in this series has 8 inputs, with

many DSP blocks and Ram blocks which can be used as FIFO dual-port RAM or shift registers(Corporation, 2004)(Altera, 2010).

The Arria series: This series also based on 8-input LUT like the Stratix series. The series is normally utilized for serial communication applications that need a high-performance because it has very high-speed transceiver hardware blocks which are embedded on its internal design. The other characteristics of the Arria FPGA devices are similar to the Stratix devices(Corporation, 2012).

Table 2:2 summarizes characteristics of different Altera series.

| Family         | Process<br>(nm) | LUT Size | Logic Cells   | RAM (bits)  | Number of<br>DSP Blocks | HC-Processor |

|----------------|-----------------|----------|---------------|-------------|-------------------------|--------------|

| Excalibur      | 180             | 4        | 4 k–34 k      | 32 K-256 K  | -                       | ARM922T      |

| Cyclone        | 130             | 4        | 2.9 k-20 k    | 58 K–288 K  | -                       | -            |

| Cyclone II     | 90              | 4        | 4.6 k–64 k    | 117 K-1.1 M | 13-150                  | -            |

| Cyclone<br>III | 65              | 4        | 5.2 k–119 k   | 414 K-3.8 M | 23-288                  | -            |

| Cyclone<br>IV  | 60              | 4        | 6.3 k–150 k   | 270 K-6.3 M | 15-266                  | 100          |

| Arria GX       | 90              | 8        | 8 k–36 k      | 1.2 M-4.3 M | 10-44                   | -            |

| Arria II<br>GX | 40              | 8        | 6 k–102 k     | 783 K-8.3 M | 29–92                   | -            |

| Stratix        | 130             | 4        | 10 k–79 k     | 899 K-7 M   | 6-22                    | -            |

| Stratix II     | 90              | 8        | 6 k–72 k      | 410 K-8.9 M | 12-96                   |              |

| Stratix III    | 65              | 8        | 19 k–135 k    | 1.8 M-14 M  | 27-112                  | -            |

| Stratix IV     | 40              | 8        | 29 k–325 k    | 6.3 M-22 M  | 48-161                  |              |

| Stratix V      | 28              | 8        | 239 k-1,087 k | 29 M-53 M   | 200-1,840               | -            |

Table 2.2. Characteristics of Different Altera Series.

#### 2.6. Xilinx Zinq

Xilinx Zynq is a new generation of FPGA System-on-Chip (SoC). The Zynq devices are primarily manufactured to be used for variety kind of applications because its high flexibility. The device has an embedded dual-core ARM Cortex-A9 processor which build in the internal fabric of FPGA logic.

The dual-core ARM processor in Zynq devices has the capability to run full operating systems whereas the other programmable logics are based on 7-series of the Xilinx FPGA internal architecture (Capability, 2016). The AXI interfaces (Advanced eXtensible Interface) are used to build the Zynq architecture, that supply low-latency

connections and high bandwidth between the main elements of the device(Reference, Axi, & Guide, 2014). In other word, the Processing System (PS) part and the Programmable Logic (PL) part can perform the related functions individually without any conflict or overhead between two separate parts. That means, simplifying the system architecture leads to reductions in size and overall cost.

# 2.6.1. System-on-Chip with Zynq

The concept behind the System-on-Chip is that: a single Integrated Circuit (IC) chip can be utilized to perform all functionality of the hardware system, compared with traditional circuits that need several chips for each function. The term of the SoC normally can be represented as an Application Specific Integrated Circuit (ASIC), that could comprise from analog circuits, digital logic, and other communication components such as radio frequency elements in addition to the digital-to-analog (DACs) and analog-to-digital converters (ADCs) embedded in a signal Integrated Circuit.

From the digital aspect of SoC, the SoC can include all aspects related to a digital system such as memories, microprocessors, interface circuits, high-speed digital elements, and so on. Otherwise, we might need separate devices to realize each function. The SoC technique provides:

- lower cost,

- low power consumption,

- high-level of design security,

- fast-rate of data transfers among the system components,

- small size, and

- high reliability.

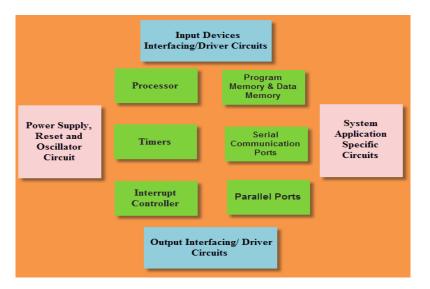

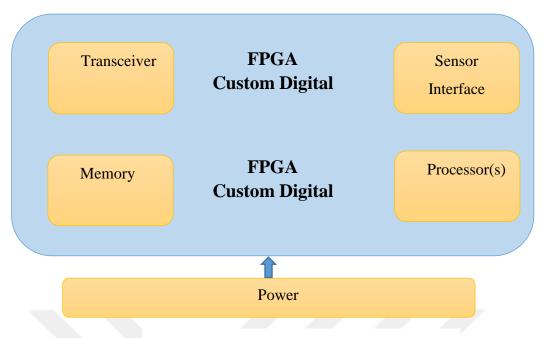

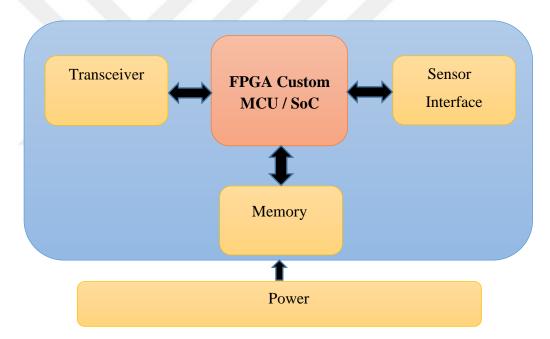

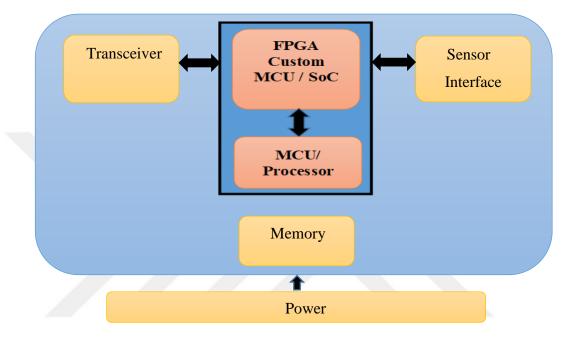

A simple graphical diagram of the System-on-Chip is demonstrated in Figure 2.5 (Xilinx, 2018).

Figure 2.5. Diagram of the System-on-Chip

On the other hand, the ASIC-based SoCs are suffering from disadvantages such as:

- (i) The flexibility of the system is low.

- (ii) The development of the SoCs system is very high speed and time consumption.

The high cost of system development making this kind of non-recurring engineering effort (and cost) of developing an ASIC are significant, making this type of hardware system suitable only for the application and systems that don't need any future upgrades. Mobile phones, tablets, and PCs are an example of the devices that comprise processors based of ASIC; These kinds of processors normally comprise single or multiple processor cores, interfacing circuits, storage units, and other associated elements (John and Smith, 1997).

All these limitations of ASIC-based SoCs make them incompatible for many significant applications that need the ability of system upgrade and a high level of flexibility. Is it clear the important of the flexibility in our life applications so, motivates the hardware designers to move towards re-programmable devices based SoCs in order to add more flexibility to add the ability of upgrades the functionality of the system and saving the time and cost. Field-Programmable Gate Array (FPGA) is the natural solution and one of the most common examples of re-programmable devices.

FPGAs are adaptable devices which can be programmed to actualize any subjective system. Compared with ASICs devices, the FPGAs offering high-level performance

and more flexible hardware platform that can be configured to achieve any desired digital system. There is no risk and very easy when system upgrading is necessary to the latest generation of Xilinx's all-programmable System-on-Chip (SoC).

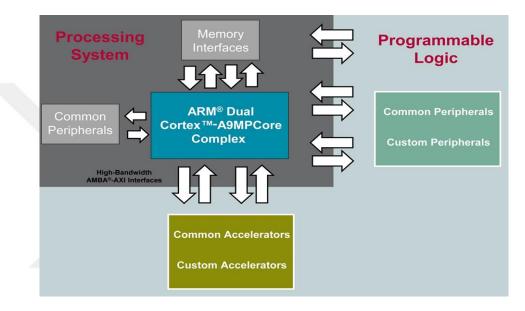

Now, the FPGA-based Zynq device gives a considerably more perfect hardware platform for actualizing adaptable SoCs: the Xilinx presents the Zynq device which is the latest generation of Xilinx as a kind of all-programmable System-on-Chip (APSoC), that superbly catches its abilities. The internal architecture of the Zynq is presented in Figure 2.6 (Xilinx, 2018).

Figure 2.6. Internal Architecture of Zynq Device.

According to Figure 2.6, the internal architecture of the Zynq consists mainly of two parts: Processing System (PS) which comprises the dual-core ARM Cortex-A9 processors in addition to the multiple common peripherals and memory interfacing. and the second part is Programmable Logic (PL), that is equivalent to the traditional FPGA fabric (internal structure) and has a long range of general peripherals such as General-Purpose Input /Output (GPIO), different kind of memories, A/D converters, communications interfaces, and so on. The two parts of Zynq architecture can work together or independently.

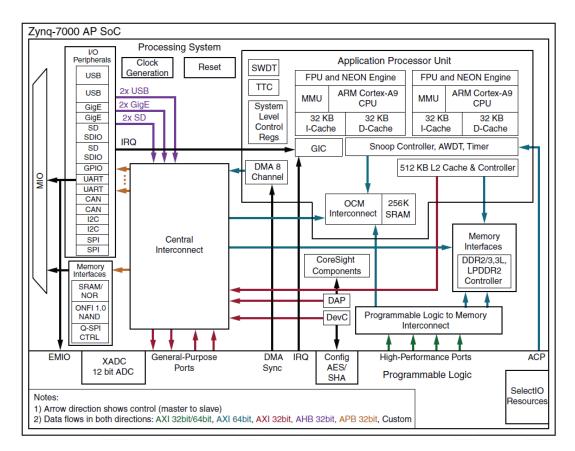

## 2.6.2. Processing System (PS)

The Zynq processing system includes ARM processor with many associated hardware processing resources constructing the Application Processing Unit (APU), in addition to memory interfaces, clock generation, cache memory, group of peripheral interfaces,

and high-performance interconnection (Xilinx, 2015). Figure 2.7 demonstrates the diagram of the Zynq PS (Xilinx, 2018).

Figure 2.7. Diagram of the Zynq PS.

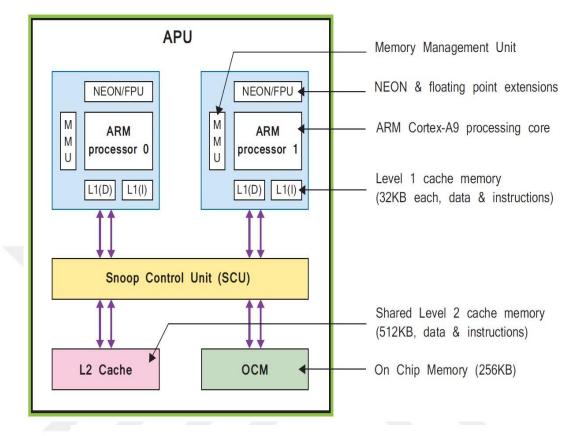

The frequency of the ARM processor is up to 1GHz, based on the series of the Zynq device. Each dual-core of ARM Cortex-A9 processor has two levels of cache memory: Level 1 and Level 2 caches. The size of Level 1 is 32KB which is used for data and instructions. This amount of cache is used to reduce the access time of the data and instruction that are frequently required and optimize the performance of the processor. While the size of Level 2 cache memory is 512KB which is shared between two core processors in addition to 256KB of on-chip cache within the APU.

On the other hand, the Software Development Kit (SDK) from Xilinx is used to configure the ARM processor which comprises all necessary tools and libraries to develop the processor's functions.

Beside the ARM processor, the APU has NEON engine which utilize to provide Single Instruction Multiple Data (SIMD) mechanism to enhance the processing of multimedia (2D/3D graphics, video, audio, user interface, etc.) and Digital Signal Processing (DSP) (Manual, 2015). Figure 2.8 explains the location of the NEON engine within the APU (Xilinx, 2018).

Figure 2.8. Location of the NEON engine within the APU.

## 2.6.3. The External Interfaces of Processing System

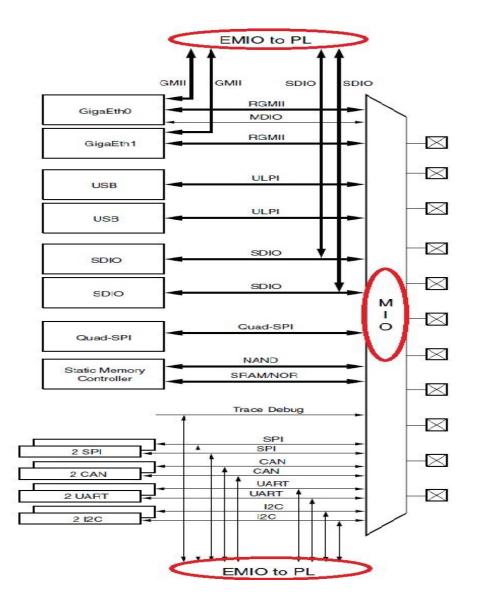

There is a diversity of interfaces that are used by the Zynq PS to communicate the PL and the external devices as shown in Figure 2.7. According to the Figure 2.7, the Multiplexed Input / Output (MIO) are utilized to bind the PS part and external components. The MIO circuit is a flexible connectivity that consists of 54-pins which can be used to achieve different functions. The external connection also can be done by the extended MIO (EMIO) which is 192-signals (64 Inputs, 128 outputs) indirect connection from PS part to external environment through Zynq PL(Xilinx Inc. SDK, 2016). The MIO and EMIO demonstrated in Figure 2.9.

Figure 2.9. MIO and EMIO Interface.

The EMIO signals are normally utilized when any IP block core within the PL wants to access the PS part or more then 54-MIO is needed for any hardware design. The I/O ports within the MIO or EMIO consist of standard interface circuits, and (GPIO) that can be utilized for a long range of applications which comprise switches, and LEDs, etc. (Xilinx, 2018). The overall I/O peripheral is shown in Table 2.3 which include the standard name of each peripheral and its description.

| I/O Interface | Description                                                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI (x2)      | Serial Peripheral Interface [10]<br>De facto standard for serial communications based on a 4-pin<br>interface. Can be used either in master or slave mode.                                |

| I2C (x2)      | I <sup>2</sup> C bus [14]<br>Compliant with the I2C bus specification, version 2. Supports<br>master and slave modes.                                                                     |

| CAN (x2)      | Controller Area Network<br>Bus interface controller compliant with ISO 118980-1, CAN<br>2.0A and CAN 2.0B standards.                                                                      |

| UART (x2)     | Universal Asynchronous Receiver Transmitter<br>Low rate data modem interface for serial communication. Often<br>used for Terminal connections to a host PC.                               |

| GPIO          | General Purpose Input/Output<br>There are 4 banks GPIO, each of 32 bits.                                                                                                                  |

| SD (x2)       | For interfacing with SD card memory.                                                                                                                                                      |

| USB (x2)      | Universal Serial Bus<br>Compliant with USB 2.0, and can be used as a host, device, or<br>flexibly ("on-the-go" or OTG mode, meaning that it can switch<br>between host and device modes). |

| GigE (x2)     | Ethernet<br>Ethernet MAC peripheral, supporting 10Mbps, 100Mbps and<br>1Gbps modes.                                                                                                       |

Table 2.3. I/O Peripheral Description.

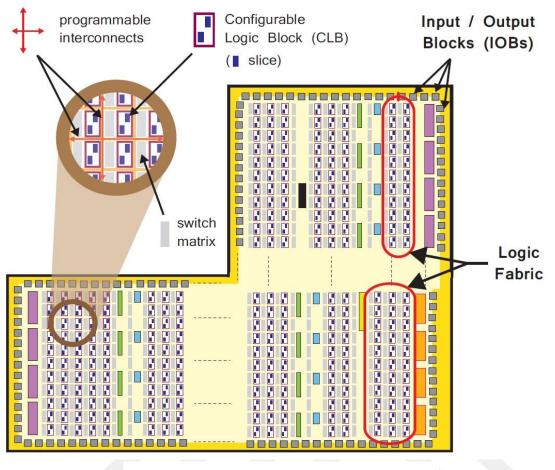

# 2.6.4 Programmable Logic

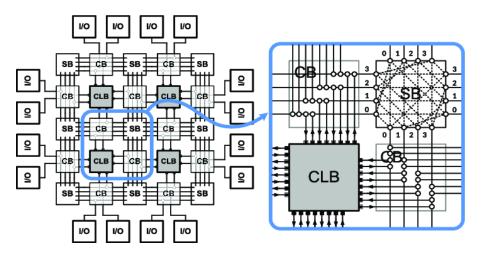

The programmable logic (PL) is the second portion of the Zynq architecture. Figure 2.10 shows the main elements that can be included within this part. The PL part represents the general logic of the FPGA fabric. Generally, the Zynq PL is like any traditional FPGA device. It consists of general Input/Output Blocks (IOBs), Configurable Logic Blocks (CLBs), and programmable interconnection which is used to connect the internal parts of PL.

Figure 2.10. Zynq PL structure.

Based on Figure 2.10, all features of the PL can be abridged as shown below:

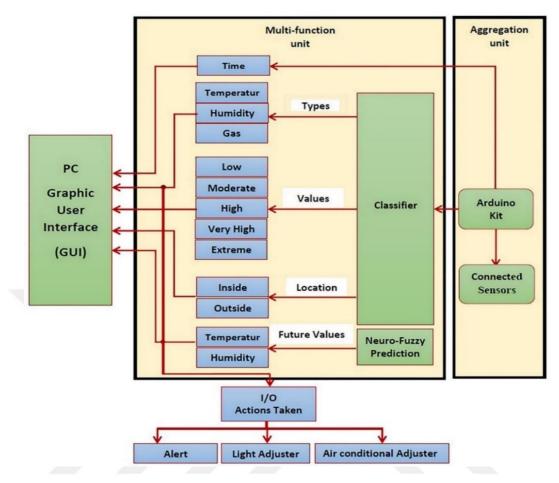

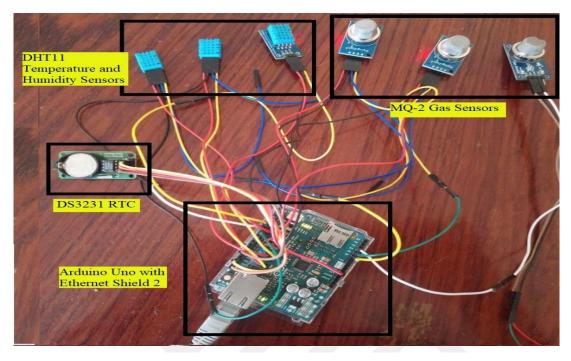

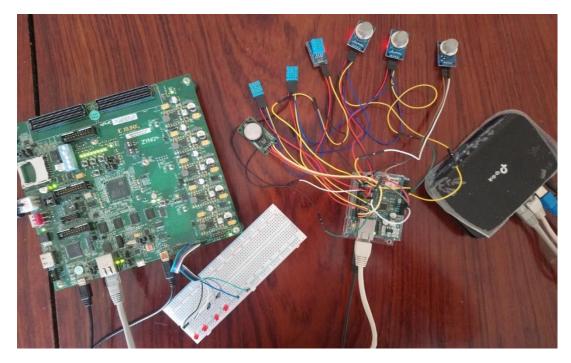

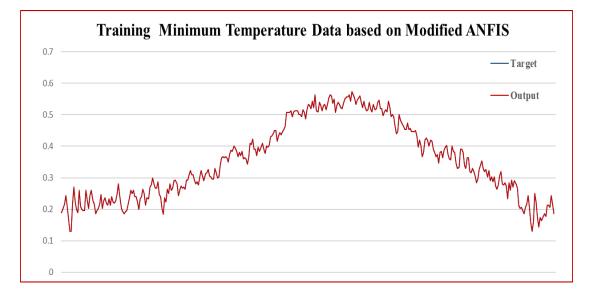

- Configurable Logic Block (CLB): The CLB is the basic logic element on the FPGA fabric. The general structure of the CLB consists of smaller logic element components, such as multiplexers, look-up tables (LUTs), and flip-flops. When connecting multiple CLB together based on switch matrix interconnection, the CLBs can be used to perform complex functions.